5K320 SATA OEM Specification

11.7 LBA High Register

This register contains Bits

When

11.8 LBA Low Register

This register contains Bits

When

11.9 LBA Mid Register

This register contains Bits

When

11.10Sector Count Register

This register contains the number of sectors of data requested to be transferred on a read or write operation between the host and the device. If the value in the register is set to 0, a count of 256 sectors (in

If the register is zero at command completion, the command was successful. If not successfully completed, the register contains the number of sectors which need to be transferred in order to complete the request.

The contents of the register are defined otherwise on some commands. These definitions are given in the command descriptions.

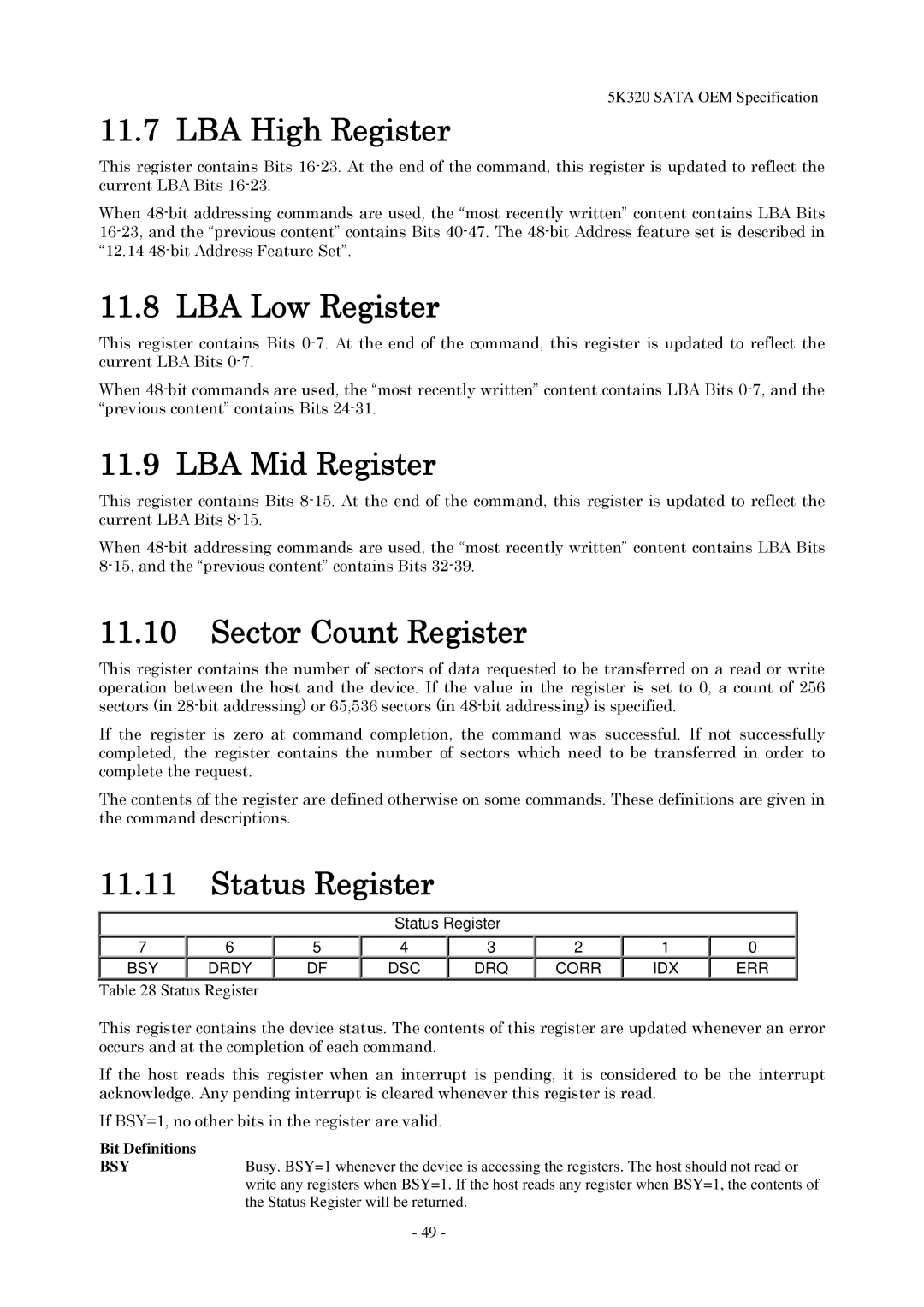

11.11Status Register

Status Register

7![]()

![]() 6

6

BSY ![]()

![]() DRDY

DRDY

Table 28 Status Register

5

DF

4

DSC

3

DRQ

2

CORR

1

IDX

0

ERR

This register contains the device status. The contents of this register are updated whenever an error occurs and at the completion of each command.

If the host reads this register when an interrupt is pending, it is considered to be the interrupt acknowledge. Any pending interrupt is cleared whenever this register is read.

If BSY=1, no other bits in the register are valid.

Bit Definitions

BSYBusy. BSY=1 whenever the device is accessing the registers. The host should not read or write any registers when BSY=1. If the host reads any register when BSY=1, the contents of the Status Register will be returned.

- 49 -