ACC Programmer’s Reference Guide

Page

Legal Notices

Page

Printing History

Ninth Edition April Release B.03.10 HP-UX

Related Documentation

Hardware Manuals

Contents

Zcom Tables and Data Structures

Zcom C I/F Library Routines

Contents

Zcom Subsystem

Introduction

Zcom Software Overview

Overview of Zcom Software Structure

Zcom

Zcom Subsystem Components

Zcom Software Overview

Zcom Concepts

Definition and Features of ZLUs

Program ZLUs

Zcom Concepts

User Interface

References

Zcom Message Handling

Overview

ZLU Definition

Mapped ZLUs

Message Queuing

Program Message Queueing

Physical Terminal Table

Priorities

Multiplexing

Outbound Multiplexing

Outbound Multiplexing

Inbound Multiplexing

Inbound Multoplexing

PTZRVR=PZLU Pzlu

Terminal State

Terminal State

Error Handling

Error Handling

Zcom Tables and Data

Zcom Tables and Data Structures

Memory Organization

Memory Organization

Differences in 32-bit and 64-bit Data Structures

Differences in 32-bit and 64-bit Data Structures

Zcom Header Structure

Hpzlu

Hpttbl

Hpptbl

Hpiftp

Zcom Header Structure

Zcom Header Structure

Zcom Header Structure

Zcom Header Structure

Zcom Header Structure

Ttgen

Zcom Header Structure

Qlbgrp

Qlbnam

Qlbqnb

Qlbrsv

Slbgrp

Slbnam

Slbsze

Slboff

Zcom Header Structure

Node Entries Table

FLAGS.event

FLAGS.valid

FLAGS.status

FLAGS.local

Node Entries Table

ZLU Tables

Individual ZLU Entries

ZLU Type Values

Type Description

ZLU Tables

Logical Terminal Tables

Ltzshrcvrs

Lthldq

Lthdqn

Ltaddr

Logical Terminal Tables

System Status flags

LTCWCT, LTTXCT, LTRXCT, Lterct Message and error counters

Logical Status Structure Ltstat

LTINST, LTBRCH, LTWORK, Ltarea Terminal logical ID

Physical Terminal Tables

Physical Terminal Tables User Maintainable Area Ptuser

Field Name Field Description Field Type Size Bytes

Physical Terminal Tables

Physical Terminal Tables

Physical Terminal Tables

Terminal Status Field Ptdrst

Firmware terminal status Ptfwst

Physical Terminal Tables

Physical Terminal Tables

Interface Table

Ifwinfo

Interface HPA Value Inhpa

63-32 31-28 27-18 17-14 13-12 10-6

Symbol Value hex Meaning

Interface Card Status Ifstat

Scheduler Event Flags Ischdl

Interface Table

Interface Table

Ipendgbufs

Isubchbuf

Ifirqbp

Nextl

Interface Table

Zcomipstatund

Zcomipstattxb

Port Configuration Buffer Iportn

Channel E1/T1 ACC Card Format

Ecode

Sync

Where

Timeslot Array Element Structure

TxSubch

TxFill

Subchannel Specification Array Element Structure

31-30 29-24 23-8

IFIRQBUF, IRESPBUF, Istdtbuf DMA response buffers

Datadelay

Response Records

Response Type Field Symbol Value Meaning

Zcomrptypebuffer

Zcomrptyperemote

Zcomrptypeirr

Response Records

Queue Header

Queue Header Area

Qlimit

Qfdata

Qfunc

Queue Header

Queue Flags

Chapter 101

Data Buffer Pool

Organization of Buffer Pool

Buffer Pool Layout when first initialized

Free Buffer Header Structure zfbhtype

Buffer flags Bfflag Field

Block Size Used flag

106

Message Header

MID

MRQ

Mstype

Msresp

Mzdest

Mzsrce

Message Type Mstype

Response code for message type 2

Response code for all other message types

Mrqcode

Mrqterm

Mrqstat

Mrqtag

Mrqcode Terminal request codes

Request Value Description

Setype

Seflag

Senode

Setime

Node Status Change Event Fields Zcomsetypenode

Nodenum

Nstat

Spare

Dynamic Reconfiguration Event Zcomsetypereconfig

Cfgclass

CFGINFO1

116

Chapter 117

Zcom Kernel Data

Ncard

Chapter 119

HPA value of I/F card Hpano

Chapter 121

SYS structure Zcom system global information, zsystype

Current Zcom system status Name Value hex State

Current Zcom system status Higher Order Bits

Name Value hex State

Debug Level Field Format

Debug Level Field Values Bit Name Value hex Meaning

Chapter 125

Zcglock

Zcmlock

Zcrlock

Zcslock

Lockp

Refcount

Zcom Kernel Data 128

Zcom C I/F Library Routines

130

ZLU configuration calls

Zltstore Logical data storage allocation

ZLU data transfer calls

Chapter 133

ZLU Definition

Man Pages

Getdevice

Getdevice Read Zcom device definitions

Considerations

Dpp Return param

Example

File, /opt/acc/cfg/zcomdevice

Multiprotocol ACC Utilities Reference

Ascii file, /opt/acc/cfg/zcomdevice.txt

Zdgen1, malloc3C

Ltfind

Description

Logical terminal table. Note that if the logical

Terminal is not found, ibuf will not contain valid data

Len Length in bytes of ibuf

142

Chapter 143

Ltqdget

Ltqdget

Posix 1003.1c kernel threads API package. This routine has

146

Ltqdput

148

Chapter 149

Makezluname

TTY Name Returned Name Comment

MYZLU01

Makezluname

Parameter and from the same TTY, the same ZLU name will be

Ptfind

154

Pointer to a buffer into which the Zcom physical

Terminal table data will be placed. Note that if

Physical terminal is not found i.e., ierr != 0, then no

Data is moved into zptt

Return Value

Zclos

Cancellation point

Chapter 159

Zcntl

Send no wait, report errors

Send no wait, report errors with buffer

Send no wait

Send no wait, definite status

Mhp

ACC Programmers’ Reference Guide Ibuf, len

Rstat

ReturnParam

For rcode not all of them are applicable to zcntl

Rtyp

164

Chapter 165

166

Zcomerror

Not a cancellation point

168

Async-cancel safe

Zcomlname

Zcomlog3x

Zcomlog

172

Int Unix error code, usually errno

Unix error string will be logged

Int Zcom error code

Zcom error string will be logged

174

Chapter 175

Zcomstatus

ACC Programmers Reference Guide under ‘ZCOM Status Message

Chapter 177

Zconfig

Zap

Return Param Response data

Chapter 181

Zcomzconfigcntl

Zcomzconfigsys

Zcomzconfigcard

Zcomzconfigport

Chapter 183

Configuration Data

Header.config

DSC Control

Header.action

No specific response data or error

Data.setctl.cfgclass

Data.setctl.cfginfo1

Zcom subsystem

Data.sysret.error

Header.tag1 Header.tag2

Data.setsys.sysname

Data.setsys.qlimit

Chapter 187

Dscreassignift

Data.setcard.iftno

Data.setcard.itype

Data.setcard.fname

Data.cardret.error

Data.cardret.iftno

Data.setport.portno

Data.setport.rcode

Data.setport.spare

Data.setport.cnfg

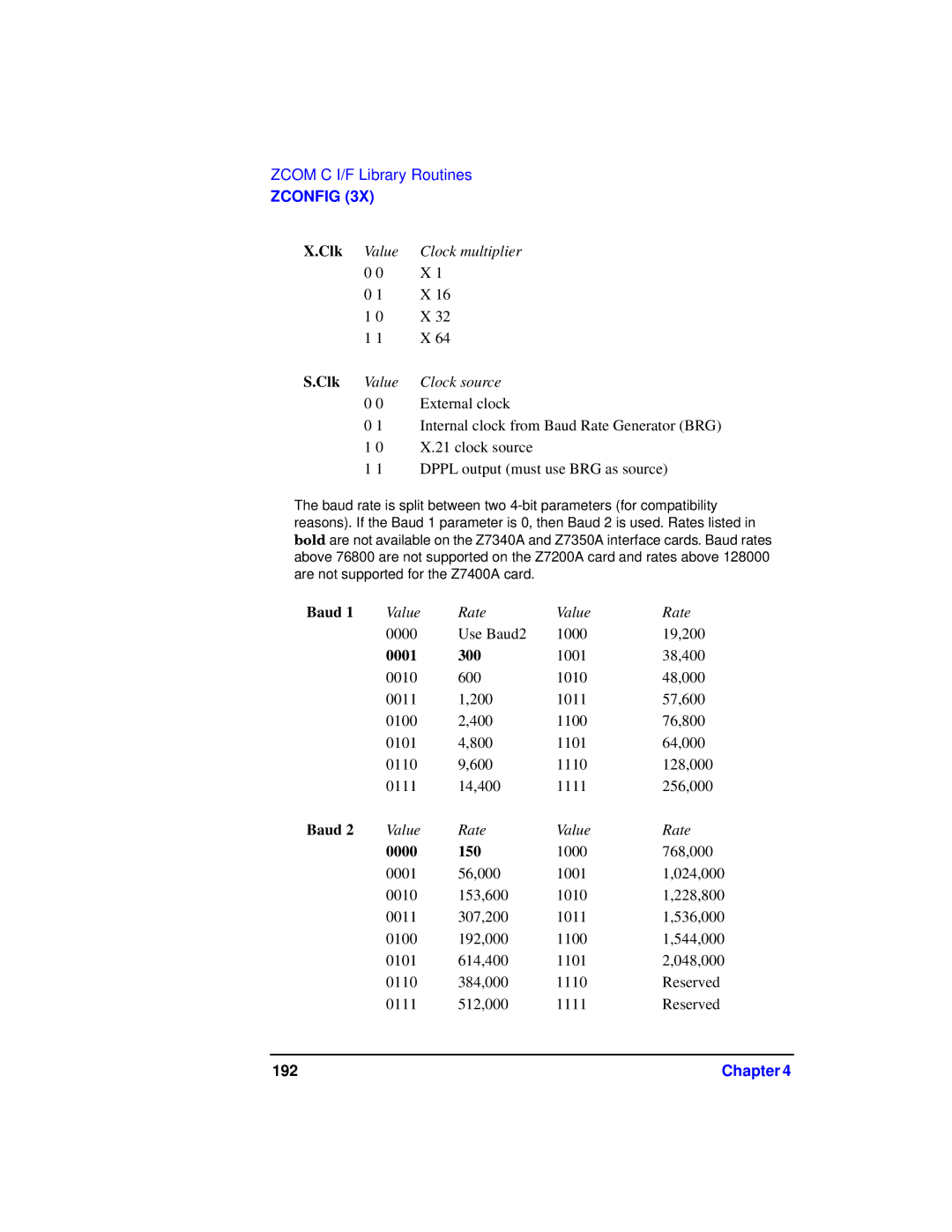

Value Encoding modes

FM1 transition = FM0 transition =

Value Parity select No Parity Odd parity Even parity

Value Clock multiplier

Value Rate 0000 Use Baud2 1000 19,200

Value Rate

Pmode Pmode2

Fsync

Value Other port for clock synchronization Port

Value T1 Transmit Attenuation Z7330B only 15 dB 22.5 dB

Otherwise by default there is a delay to avoid

T1/ESF mode contain an address which

User device. By default the ACC is a user

Performance report messages in T1/ESF mode

Data.setport.qlimit

Data.portret.iftno Data.portret.portno

Data.portret.status

Chapter 197

Configuration Data header.config

Data.setportsc.iftno

Data.setportsc.portno

Data.setportsc.subchno

Data.setportsc.rcode

Data.setportsc.ptcfg-ptinfo.subchb.tmsl

RTI

Set to Mode

Data.setportsc.ptcfg-ptinfo.subchb.spec

Set to

Data.setportsc.len

Data.portscret.status

Chapter 203

Header.action ZcDSCCREATELTTPTT Create a new terminal LTT

ZcDSCCREATELTTONPTT Create a new LTT on an existing

Data.setterm.daddr

Data.setterm.iftno

Data.setterm.portno

Data.setterm.subchno

Data.setterm.dtype

Data.setterm.ltype

Response Data data.termret.zaddr

Chapter 207

208

Name

Zeventrcvr

210

Chapter 211

‘C’ structure for a Zcom Event Message is shown below

Zcomsetypenode

Files

Zgetshrcvrlist

Zgetshrcvrlist Get list of current shared receivers

Table entry from which you want the shared receivers list

Type of shared receiver list is set to ZcMAXSHAREDRCVRS

Should have ZcMAXSHAREDRCVRS+1 entries

216

Name

Zinfo

Return

, Tables and Data Structures section

Param

Returnvalue

Files

Zinit

Zinit Zcom routine initialization

Parameters

Following fields

Chapter 223

Zltmg

Zltmg Move a logical terminal between groups

Zltmg

226

Zltmx

Zltmx Control logical terminal multiplexing

Parameters

Chapter 229

Zltqueue

Zltqueue Logical data queue allocation

Application number of terminal group

Appln

Appln Queue Returned Program Nmbr Label Queue No

Chapter 233

Zltstore

Zltstore Logical data storage allocation

Terminal table, for the storage in the extension area

236

Zltup

238

Chapter 239

Zluopen

Zcom error codes and their meanings

This return parameter is undefined

242

Zmapr

244

Zname

246

Chapter 247

Zopen

Ld1

Zap Zcom address node, ZLU number, and checksum

Node contains the local node as defined in the Ttgen

250

Chapter 251

Zpeek

Error codes and their meanings

Zread3X, zluopen3X

Zport

Zcomzmuxportall

Zcomzmuxportconf

Zcomzmuxportbaud

Zcomzmuxportport

No error

Some terminals in this port not disabled

Illegal port mode

Break routine not installed

Value Operating mode

Value Parity select

Clk

Value Clock source

258

Value Port Mode

Value

T1 ESF

260

Chapter 261

Zptup

Chapter 263

Zqmve

Chapter 265

Zqsze

Zqhdp Return param

268

Zread

Mode ZcREADWWAIT 0 Read with wait

After the timeout period has elapsed

There is no message on the queue, error Zenodata

Same ZLU. When a message arrives, only one

Chapter 271

272

Chapter 273

274

Zrntimer

276

Chapter 277

Zsend

Mhp-mid.ztagw2

Zsend

280

Chapter 281

282

Chapter 283

284

Chapter 285

286

Chapter 287

Zsetql

Chapter 289

290

Zsetrcvr

292

Zsetrcvr

294

Ztimr

296

Chapter 297

298