Appendix D: Industrial Devices

POST Checkpoint Codes

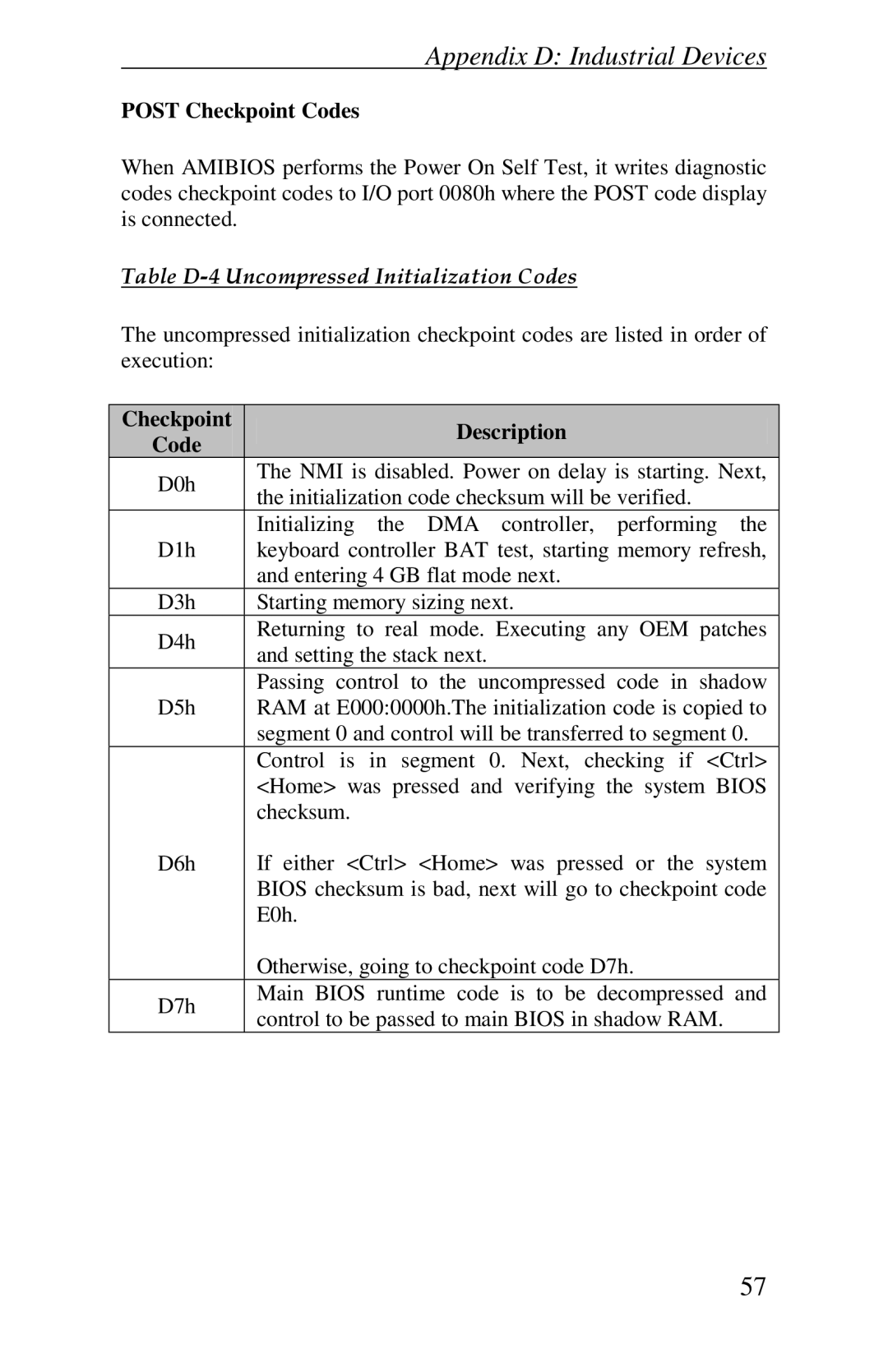

When AMIBIOS performs the Power On Self Test, it writes diagnostic codes checkpoint codes to I/O port 0080h where the POST code display is connected.

Table

The uncompressed initialization checkpoint codes are listed in order of execution:

Checkpoint | Description | |

Code | ||

| ||

D0h | The NMI is disabled. Power on delay is starting. Next, | |

the initialization code checksum will be verified. | ||

| ||

| Initializing the DMA controller, performing the | |

D1h | keyboard controller BAT test, starting memory refresh, | |

| and entering 4 GB flat mode next. | |

D3h | Starting memory sizing next. | |

D4h | Returning to real mode. Executing any OEM patches | |

and setting the stack next. | ||

| ||

| Passing control to the uncompressed code in shadow | |

D5h | RAM at E000:0000h.The initialization code is copied to | |

| segment 0 and control will be transferred to segment 0. | |

| Control is in segment 0. Next, checking if <Ctrl> | |

| <Home> was pressed and verifying the system BIOS | |

| checksum. | |

D6h | If either <Ctrl> <Home> was pressed or the system | |

| BIOS checksum is bad, next will go to checkpoint code | |

| E0h. | |

| Otherwise, going to checkpoint code D7h. | |

D7h | Main BIOS runtime code is to be decompressed and | |

control to be passed to main BIOS in shadow RAM. | ||

|

57