Personal Computer Model Z-350

BACKUP, INIT, COPY, DEBUG, Killall

Timer

Memory

Video

Slot Slot2

Refer to the page TIN Circuit Diagram

LSI, 1C Cmosic

SFDI/F

Symbol

Preset

Sdisp

Change Disp

Base

Basic Area RAM

System

User

MZ-1D07

MZ3500 System configuration of Model

MS1 = D MSO = 0 L

Software Memory Configuration

Timing of Reset Signal

ROM-IPL

SD1 System Loading & CP/M

MAO

Bank Select

Ffff

Operational description

SD3 RAM based Basic

Bank

ROM

Main Memory Mapper

Block diagram Relation between MMR main memory

Table below describes address map

Main CPU and I/O port

This paragraph discusses main CPU I/O

Main CPU \m

0001

MZ3500

Sub CPU and I/O port

To Reset

Memory mapper MMRSP6102R-001 Block diagram

Address BUS

Coab

Srdy

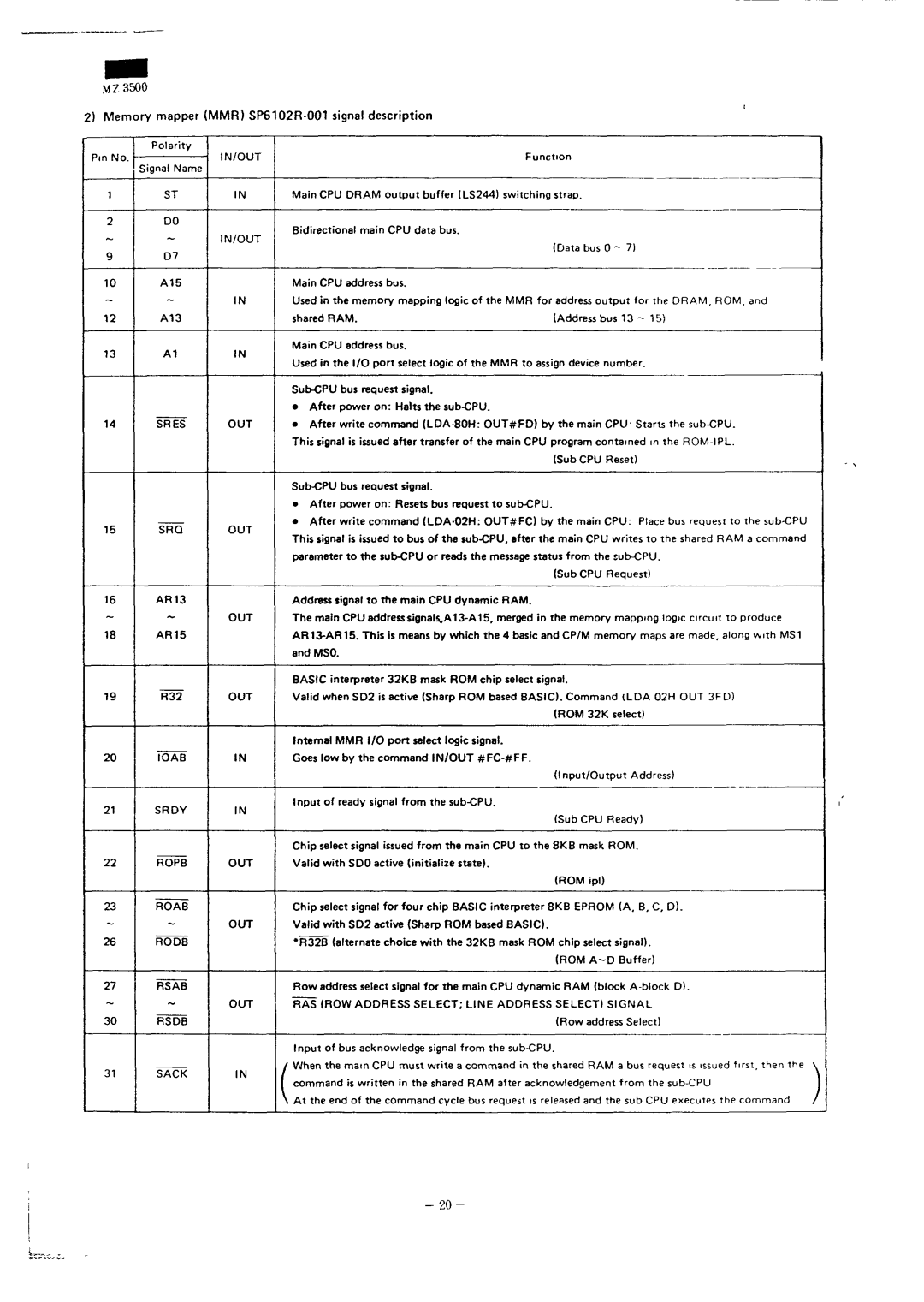

MZ3500 Memory mapper MMR SP6102R-001 signal description

RAS ROW Address Select Line Address Select Signal

Pin No

RO2B

IN/OUT

RO1B

1 1 1 1 0 KI1 Dl Do 17 D6 D5

A7 A6 A5A4A3A2AlAO H E X Uhus 1 O

D2 Dl 1 1 1 1 1 0 FE do D4 D3

1 1 1 1 1 1 FF 14 I N D3

MZ3500 Memory ROMIPL, RAMCOM, S-RAM select circuit

CRT

Specification

Asci

Summary of video display specification

Blue

Dot pitch

Dot color designated by

Graphic dot

CH AI +,! AT A r + + G

CH AT

KA7

Ascii CG

#1 FFF

Video RAM Structure of Vram

#0000

Structure of character Vram When read/write from GDC

#07FFA

8bit

Read/write by Z-80 via the GDC 640 x 200 dots display mode

FV = 60 Hz

16K

Setup of GCD master/slave

640 x 400 bits display mode FH = 20.92 kHz FV = 47.3 Hz

Master/slave setup by combination

O signal switching

Graphic V-RAM Address

Crtc block diagram

Page

Master slice LSI CSP-1 SP6102C 002 signal description

CSH

CSP-1 Block Diagram

» CK

HSY2 2BLK2

LSI CSP-2 SP6012C-003 Signal Description

3r00

CSP 2 Block Diagram

DSP2 OUT

CAS OUT

GDC Graphic display controller UPD7220 signal description

NK-CLC

AD15ILC2

AT~BTI

CSR-1MAGE

Structure

CG Address Select Circuit

Circuit description

Vsync

Blsc

Character Vram select circuit

Read/write from the Z-80 to V-RAM

Set GDC command code

Csrw C 49H -COMMAND Code

Return when all parameters were sent

Write C 23H Command Code Vecte C 6CH Command Code

Fifo Empty?

Explanation

60H

VECTE. Dot address is structured on the screen

Following manner Dot display program example-1

Kind of line solid line

I T E C 23H

P4 88H P5 HH

Outline

Floppy disk

TJ ILJ n

Ci D ci Ici

VnVn n nV nnn7

Data

MZ3500 MFD interface block diagram

22 «- o Window

FDC UPD765

UPD765 signal description

MZ350C

Trigger motor on of the timer 555 Selects FDD

Port used in the MFD interface is as follows

MFM recording method

Media detection

Controls during read, write, seek, and re- calibrate

3500 Precompensate Circuit

Control during seek and recalibration

Purpose String of data Pulses from the FDD Data window

VFO circuit

Filter Phase Detector Amplifier Window

VFO circuit configuration

BQA

MFM Mode

FM mode timing chart

\\\\

3DSC

Side =

Aload

\128

76 iy 7 EH 77 / FFH

Track 10 sector

Indicates the byte position From the top of directory

B144 6145 B146 B147 39 B148 B149 B150 B151

Ii Patat

39 B74 B75

1015

Data transmission format

General specification

MZS500

Example 7-bits, even parity, 1 stop bit

OFF

AC controls

Start

8251 AC

MZ3500 Data output control

KTS

RXEN,UTR , T X E N

3SOO

9 6.3

200

256

128

«--N

Wl -»

8253 OUT

8253

AA3

Printer interfacing circuit

DAT

DS7

Data transfer timing

General description of the parallel interface

Output

I/O port map

Read Hold

Clock circuit Schematic

Write Hold SET

DIN

LSB MSB

MZ3500 PD1990AC Block diagram

» GETE1 J

Mmmil

S I C

3500

GP I/O

SFD 1/F

Dipswa

SW2 SW1 On on CE332P OFF on MZ1P02 On OFF IO2824 OFF OFF

SEC

FD2

\f Canbe in either state

Description of each block

Block diagram

Functions

+5V

Switching regulator

Timing chart

Alarm generation circuit

Key

Specification of keyboard control

At rrn

2s 2s22 21

Key search timing

Key

Strobe

Protocol Key to sub CPU

132.5

22.5/-s

Keyboard controller basic flow

XTAL1 XTAL2 Reset INT

Keyboard controller signal description

PIN

ALE DBO DB7 GND

On OFF

Sub-CPU side

Procedure

CRT inter face test

Shared RAM

Abnormal

S C I I 00-FF

Ready O.H

Abnormal test ending

1 5 c * O DR O.7

ROM-IPL Main CPU Checker Flow Chart 1/2

100

Main CPU Checker Flow Chart M?

M7*500

101

Keyboard test

Keyboard controller ROM test

IPL Flow Chart

SEEK, Read Error

Jump \ Boot Address System

Error

Load Iocs SEEK& Read

105

SUB CPU IPL Flow Chart

R R R R F1

LJ LJ LJ LJ LJ LJ LJ

U J l J J L i J L L j l J J L l J L L l

LU LU U LJ LlJ LJ U U

RoB

IwC

AIO

MZ-35OO Parts Guide LI

S C R I P T I O N

No Parts Code

LED PWB

IE--or Ooss-zw

Parts Code

MZ-3500

N T K

Qcnw

S C R I P T I O N

Connector

NO. Parts Code

MZ-3500

Parts Code

A a N a D

NEW

VH S N 7 4 0 6 N

Coos

Part S C R I P T I O N

Mark Rank

M2-3500

J9, MZ1K02,1K03,1K04,1K05 Key unit

LSI RAM

SOC

LA a

NO. Parts Code

D e

Tin

N a a

Parts Code

MZ-3500

Sharp Corporation