MZ3500

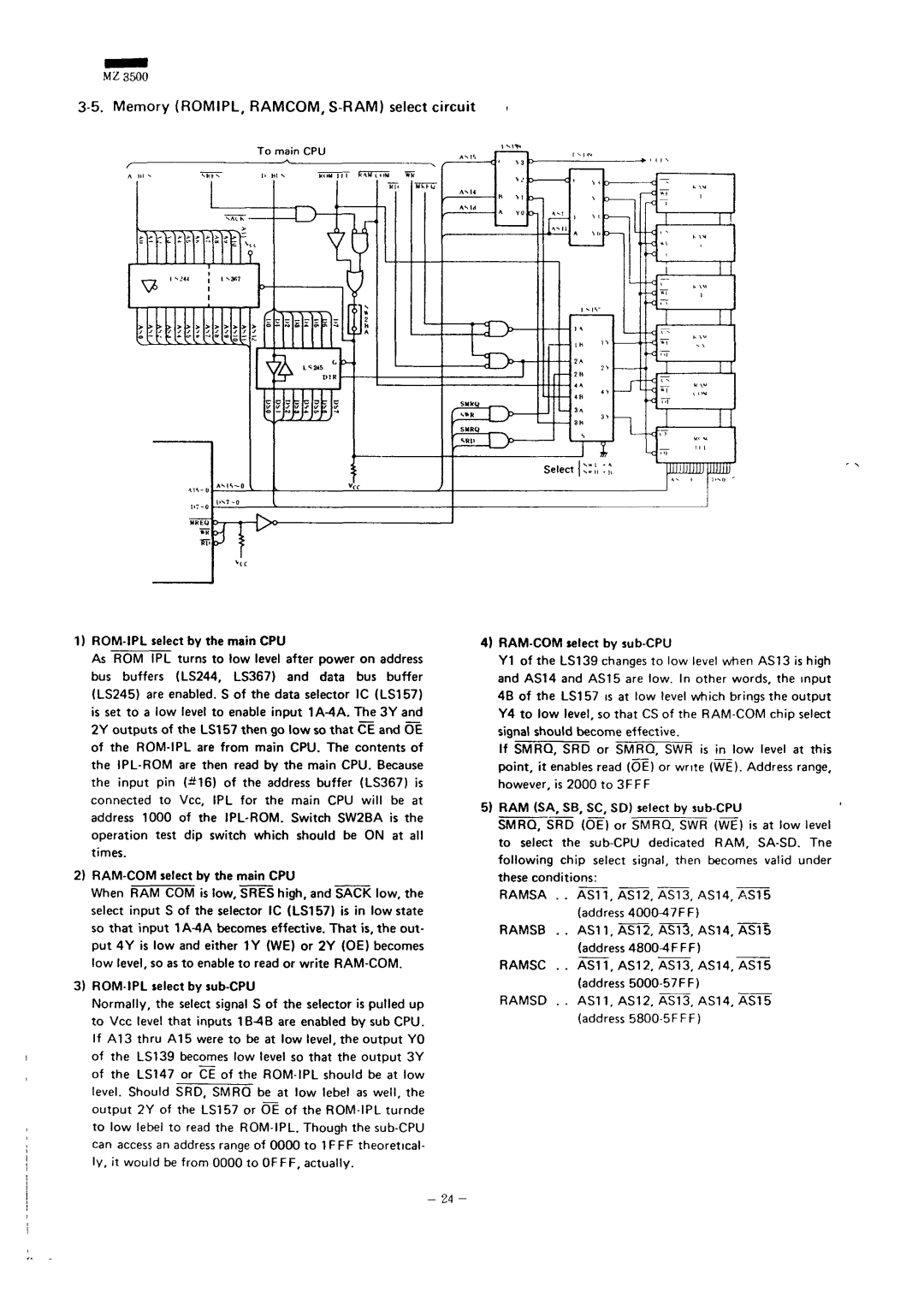

3-5. Memory (ROMIPL, RAMCOM, S-RAM) select circuit

To main CPU

1)

As ROM IPL turns to low level after power on address bus buffers (LS244, LS367) and data bus buffer (LS245) are enabled. S of the data selector 1C (LS157) is set to a low level to enable input

2)

When RAM COM is low, SRES high, and SACK low, the select input S of the selector 1C (LS157) is in low state so that input

3)

Normally, the select signal S of the selector is pulled up to Vcc level that inputs

4)

Y1 of the LS139 changes to low level when AS13 is high and AS14 and AS15 are low. In other words, the input 4B of the LS157 is at low level which brings the output Y4 to low level, so that CSof the

If SMRQ, SRD or SMRQ, SWR is in low level at this point, it enables read (OE) or write (WE). Address range, however, is 2000 to 3FFF

5)RAM (SA, SB, SC, SD) select by

SMRQ, SRD (Of) or SMRQ, SWR (WE) is at low level to select the

RAMSA .. ASVi, AS12, AS13, AS14, AST! (address 4000^17FF)

RAMSB .. AS11, AST2, AST3, AS14, AS15 (address

RAMSC .. AS11, AS12, AS13, AS14, AS15 (address

RAMSD .. AS11, AS12, AS13, ASK, ASHi (address

- 24 -