Table

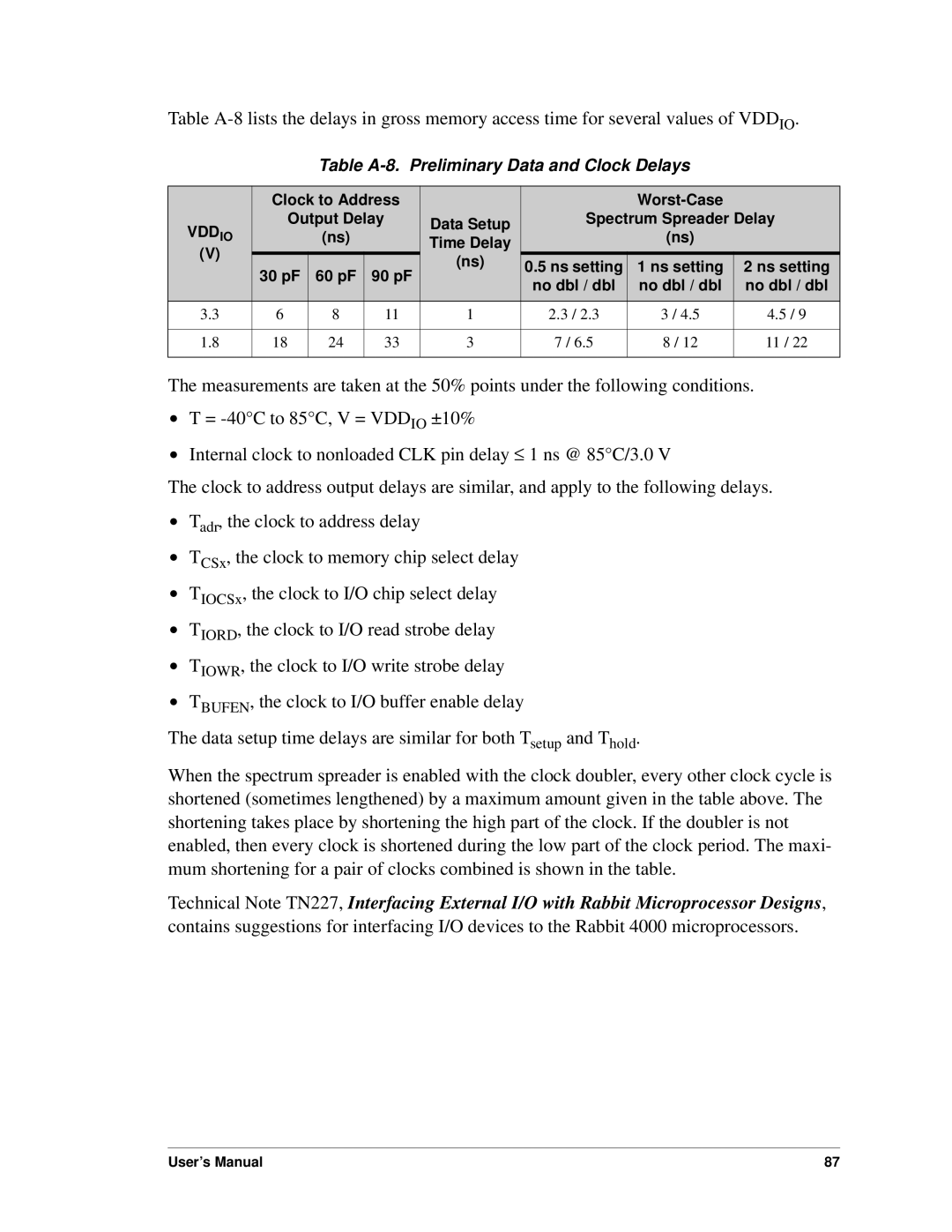

Table A-8. Preliminary Data and Clock Delays

| Clock to Address |

|

|

|

| |||

VDDIO | Output Delay | Data Setup | Spectrum Spreader Delay | |||||

| (ns) |

|

| (ns) |

| |||

|

| Time Delay |

|

| ||||

(V) |

|

|

|

|

|

| ||

30 pF | 60 pF | 90 pF | (ns) | 0.5 ns setting | 1 ns setting | 2 ns setting | ||

| ||||||||

|

| |||||||

|

| no dbl / dbl | no dbl / dbl | no dbl / dbl | ||||

|

|

|

|

| ||||

3.3 | 6 | 8 | 11 | 1 | 2.3 / 2.3 | 3 / 4.5 | 4.5 / 9 | |

|

|

|

|

|

|

|

| |

1.8 | 18 | 24 | 33 | 3 | 7 / 6.5 | 8 / 12 | 11 / 22 | |

|

|

|

|

|

|

|

| |

The measurements are taken at the 50% points under the following conditions.

•T =

•Internal clock to nonloaded CLK pin delay ≤ 1 ns @ 85°C/3.0 V

The clock to address output delays are similar, and apply to the following delays.

•Tadr, the clock to address delay

•TCSx, the clock to memory chip select delay

•TIOCSx, the clock to I/O chip select delay

•TIORD, the clock to I/O read strobe delay

•TIOWR, the clock to I/O write strobe delay

•TBUFEN, the clock to I/O buffer enable delay

The data setup time delays are similar for both Tsetup and Thold.

When the spectrum spreader is enabled with the clock doubler, every other clock cycle is shortened (sometimes lengthened) by a maximum amount given in the table above. The shortening takes place by shortening the high part of the clock. If the doubler is not enabled, then every clock is shortened during the low part of the clock period. The maxi- mum shortening for a pair of clocks combined is shown in the table.

Technical Note TN227, Interfacing External I/O with Rabbit Microprocessor Designs, contains suggestions for interfacing I/O devices to the Rabbit 4000 microprocessors.

User’s Manual | 87 |