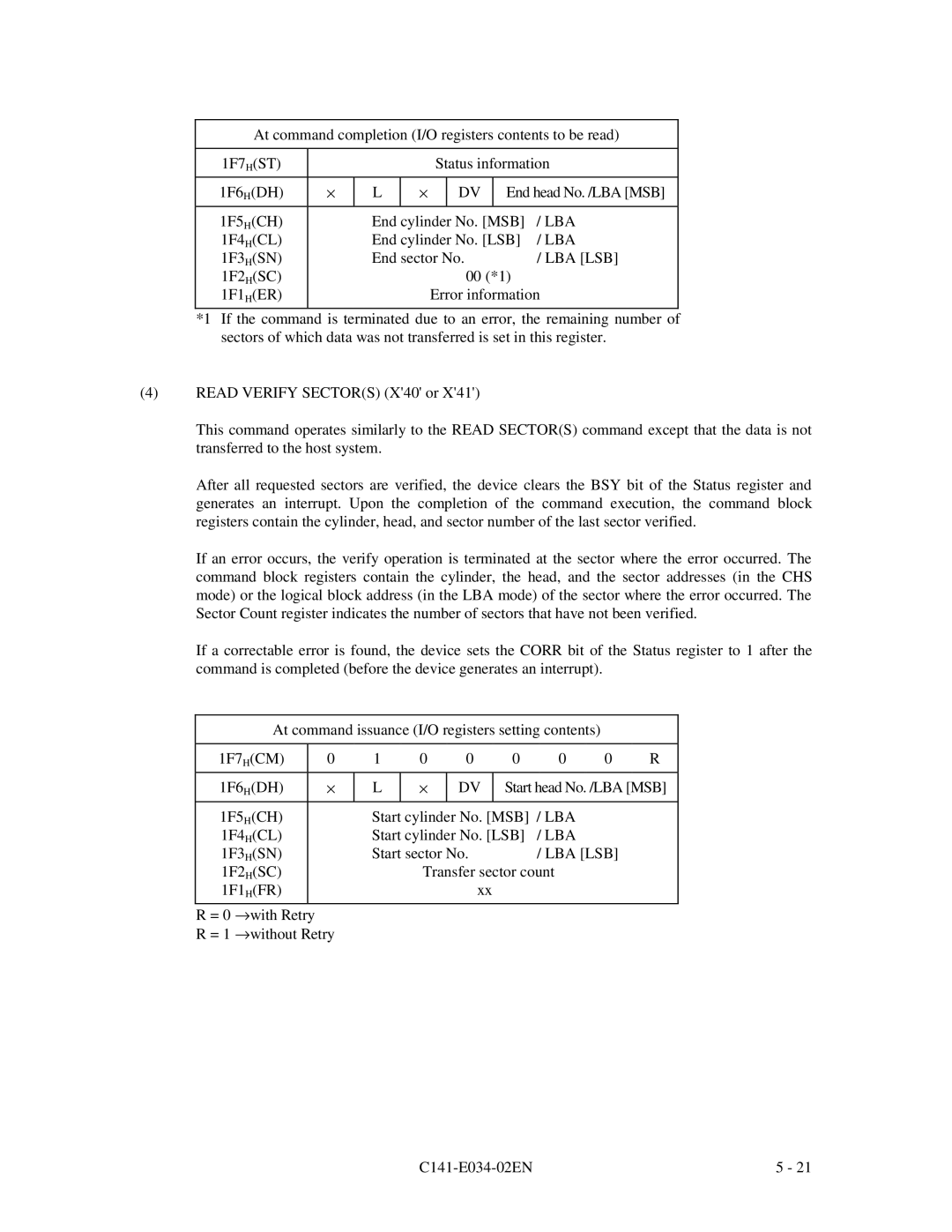

At command completion (I/O registers contents to be read)

1F7H(ST) |

|

|

| Status information | ||||

|

|

|

|

|

|

|

| |

1F6H(DH) | × | L | × |

| DV |

| End head No. /LBA [MSB] | |

|

|

|

|

|

|

| ||

1F5H(CH) |

| End cylinder No. [MSB] | / LBA | |||||

1F4H(CL) |

| End cylinder No. [LSB] | / LBA | |||||

1F3H(SN) |

| End sector No. |

|

| / LBA [LSB] | |||

1F2H(SC) |

|

|

| 00 | (*1) |

| ||

1F1H(ER) |

|

|

| Error information | ||||

*1 If the command is terminated due to an error, the remaining number of sectors of which data was not transferred is set in this register.

(4)READ VERIFY SECTOR(S) (X'40' or X'41')

This command operates similarly to the READ SECTOR(S) command except that the data is not transferred to the host system.

After all requested sectors are verified, the device clears the BSY bit of the Status register and generates an interrupt. Upon the completion of the command execution, the command block registers contain the cylinder, head, and sector number of the last sector verified.

If an error occurs, the verify operation is terminated at the sector where the error occurred. The command block registers contain the cylinder, the head, and the sector addresses (in the CHS mode) or the logical block address (in the LBA mode) of the sector where the error occurred. The Sector Count register indicates the number of sectors that have not been verified.

If a correctable error is found, the device sets the CORR bit of the Status register to 1 after the command is completed (before the device generates an interrupt).

At command issuance (I/O registers setting contents)

1F7H(CM) | 0 | 1 | 0 | 0 | 0 | 0 | 0 | R |

1F6H(DH) | × | L | × | DV | Start head No. /LBA [MSB] | |||

|

|

|

|

|

|

|

| |

1F5H(CH) |

| Start cylinder No. [MSB] / LBA |

|

| ||||

1F4H(CL) |

| Start cylinder No. [LSB] | / LBA |

|

| |||

1F3H(SN) |

| Start sector No. |

| / LBA [LSB] |

| |||

1F2H(SC) |

|

| Transfer sector count |

|

| |||

1F1H(FR) |

|

|

| xx |

|

|

|

|

R= 0 →with Retry R = 1 →without Retry

5 - 21 |