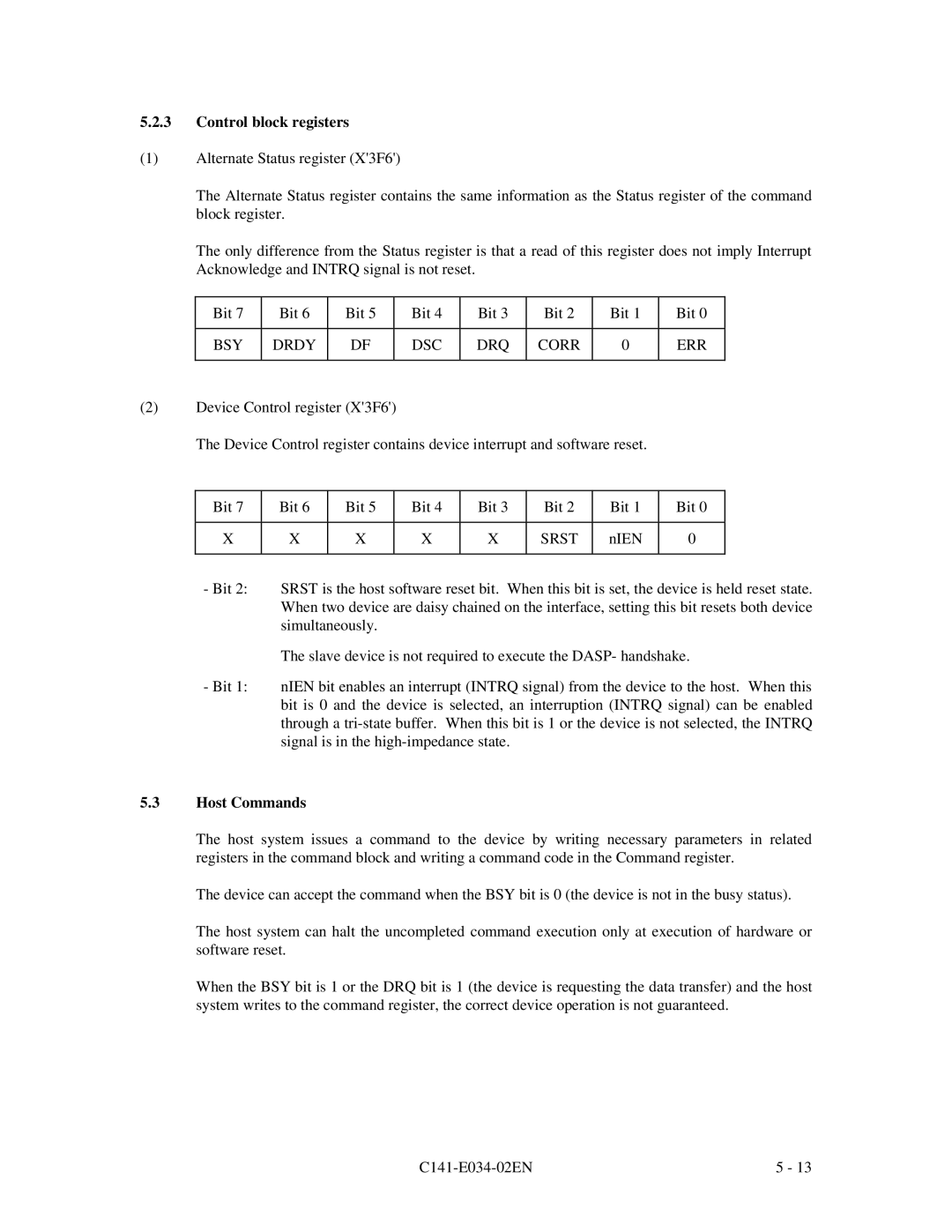

5.2.3Control block registers

(1)Alternate Status register (X'3F6')

The Alternate Status register contains the same information as the Status register of the command block register.

The only difference from the Status register is that a read of this register does not imply Interrupt Acknowledge and INTRQ signal is not reset.

Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit | 1 | Bit 0 |

|

|

|

|

|

|

|

|

|

BSY | DRDY | DF | DSC | DRQ | CORR | 0 |

| ERR |

|

|

|

|

|

|

|

|

|

(2)Device Control register (X'3F6')

The Device Control register contains device interrupt and software reset.

Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit | 0 |

|

|

|

|

|

|

|

|

|

X | X | X | X | X | SRST | nIEN | 0 |

|

|

|

|

|

|

|

|

|

|

-Bit 2: SRST is the host software reset bit. When this bit is set, the device is held reset state. When two device are daisy chained on the interface, setting this bit resets both device simultaneously.

The slave device is not required to execute the DASP- handshake.

-Bit 1: nIEN bit enables an interrupt (INTRQ signal) from the device to the host. When this bit is 0 and the device is selected, an interruption (INTRQ signal) can be enabled through a

5.3Host Commands

The host system issues a command to the device by writing necessary parameters in related registers in the command block and writing a command code in the Command register.

The device can accept the command when the BSY bit is 0 (the device is not in the busy status).

The host system can halt the uncompleted command execution only at execution of hardware or software reset.

When the BSY bit is 1 or the DRQ bit is 1 (the device is requesting the data transfer) and the host system writes to the command register, the correct device operation is not guaranteed.

5 - 13 |