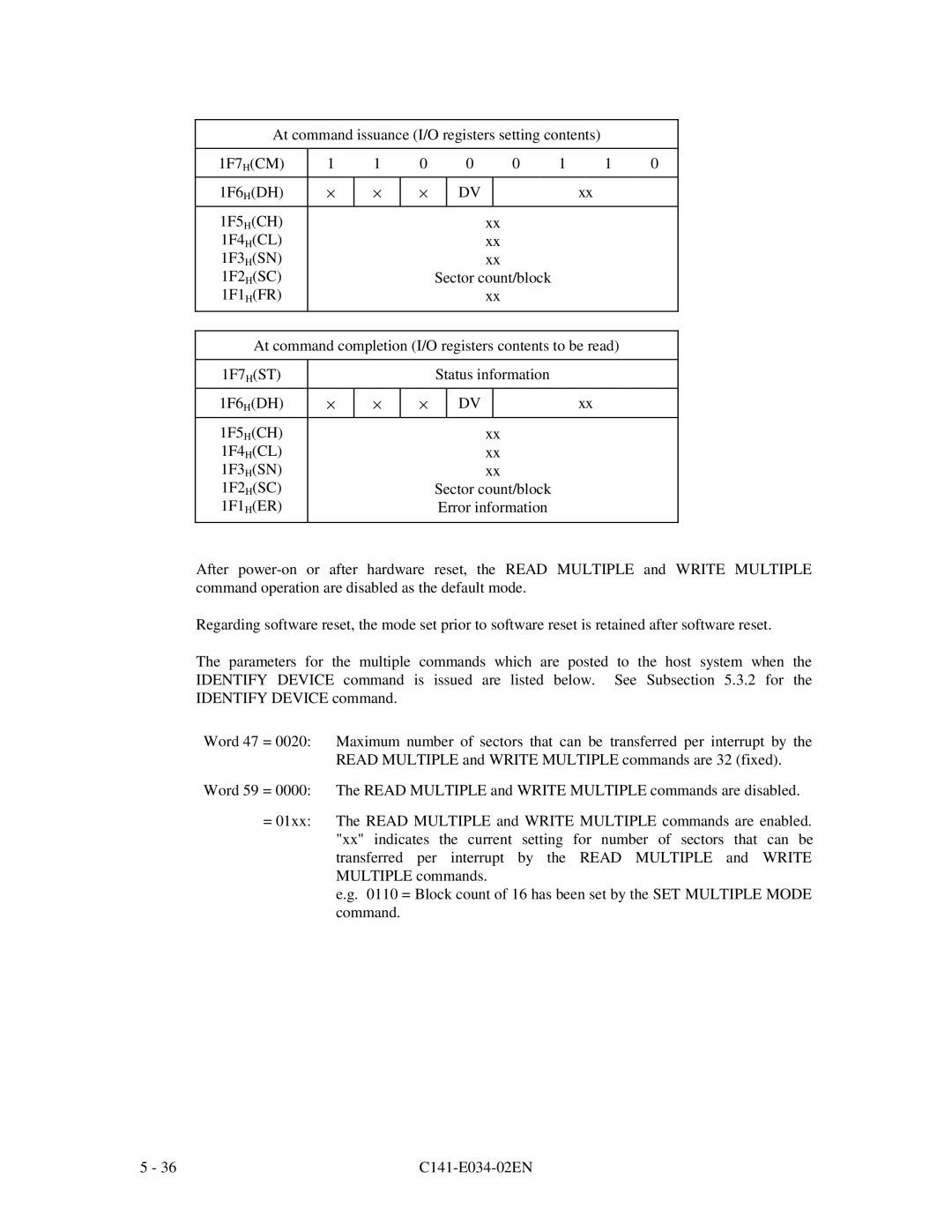

At command issuance (I/O registers setting contents)

1F7H(CM) | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | ||

|

|

|

|

|

|

|

|

|

|

|

1F6H(DH) | × | × | × |

| DV |

|

|

| xx |

|

|

|

|

|

|

|

|

|

|

|

|

1F5H(CH) |

|

|

|

|

| xx |

|

|

| |

1F4H(CL) |

|

|

|

|

| xx |

|

|

| |

1F3H(SN) |

|

|

|

|

| xx |

|

|

| |

1F2H(SC) |

|

|

| Sector count/block |

|

|

| |||

1F1H(FR) |

|

|

|

|

| xx |

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

At command completion (I/O registers contents to be read)

1F7H(ST) |

|

|

| Status information |

| ||

|

|

|

|

|

|

|

|

1F6H(DH) | × | × | × |

| DV |

| xx |

|

|

|

|

|

|

|

|

1F5H(CH) |

|

|

|

| xx |

| |

1F4H(CL) |

|

|

|

| xx |

| |

1F3H(SN) |

|

|

|

| xx |

| |

1F2H(SC) |

|

|

| Sector count/block |

| ||

1F1H(ER) |

|

|

| Error information |

| ||

|

|

|

|

|

|

|

|

After

Regarding software reset, the mode set prior to software reset is retained after software reset.

The parameters for the multiple commands which are posted to the host system when the IDENTIFY DEVICE command is issued are listed below. See Subsection 5.3.2 for the IDENTIFY DEVICE command.

Word 47 = 0020: Maximum number of sectors that can be transferred per interrupt by the READ MULTIPLE and WRITE MULTIPLE commands are 32 (fixed).

Word 59 = 0000: The READ MULTIPLE and WRITE MULTIPLE commands are disabled.

=01xx: The READ MULTIPLE and WRITE MULTIPLE commands are enabled. "xx" indicates the current setting for number of sectors that can be transferred per interrupt by the READ MULTIPLE and WRITE MULTIPLE commands.

e.g. 0110 = Block count of 16 has been set by the SET MULTIPLE MODE command.

5 - 36 |