8051 Architectural Specification and Functional Description

REGISTER | DIRECT |

Data |

REGISTER

A

REGISTER

A

REGISTER·INDIRECT | |

@R1,@RO | @DP |

(EXT DATA | (EXT DATA |

@R1,@RO

Figure 2.18. External Data Memory Move Operations

can be moved to any of these locations. Of particular interest is the Direct Address to Direct Address move which permits the value in a port to be moved to the Internal Data RAM without using any RB registers or the accumulator. The Data Pointer register can be loaded with a

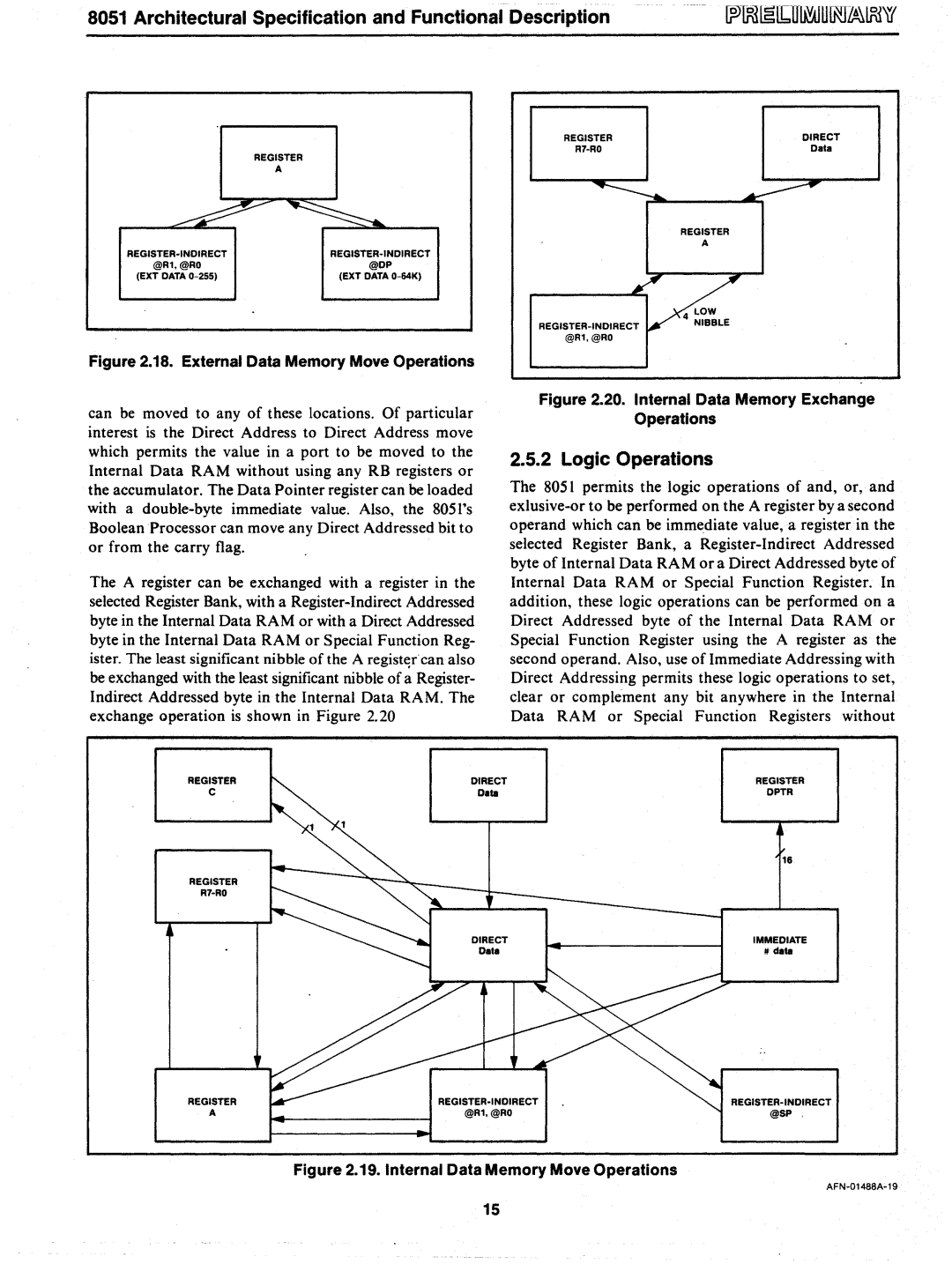

The A register can be exchanged with a register in the selected Register Bank, with a

Figure 2.20. Internal Data Memory Exchange Operations

2.5.2 Logic Operations

The 8051 permits the logic operations of and, or, and

REGISTER | DIRECT | REGISTER |

C | Data | DPTR |

16

REGISTER

DIRECT | IMMEDIATE |

Data | # data |

REGISTER | ||

A | @R1,@RO | @SP |

Figure 2.19. Internal Data Memory Move Operations

15