8051 Architectural Specification and Functional Description

Figure 2.42. The twelve period External Data Memory cycle allows the 80S 1 to use peripherals that are relatively slower than its program memories. The address is emitted from the processor during T3. Data transfer occurs on the bus during T7 through T12. TS and T6 is the period during which the direction of the bus is changed for the. read operation. The read cycle begins during T2, with the assertion of address latch enable signal ALE CD .The falling edge of ALE Q) is used to latch the address information, which is present on the bus at this time CD ' into the 8282 latch if a non-multiplexed bus is desired. At TS, the address is removed from the Port 0 bus and

the processor's bus drivers go to the high-impedance state 0. The data memor~ad control signal RD

CD ' is asserted during T7. RD causes the addressed device to enable its bus drivers to the now-released bus. At some later time, valid data will become available on the bus ® . When the 80S1 subsequently returns RD to the high level CD 'the addressed device will then float its bus drivers, relinquishing the bus again CD .

Data Memory Write Sequence (Figure 2.43)

The write cycle, like the read cycle, begins with the asser- tion of ALE CD and the emission of an address Q) . In T6, the processor emits the data to be written into the addressed data memory location CD .This data remains

valid on the bus until the end of the following bus cycle's | ||

T2 0. The write signal WR goes low at T6 | CD | and |

remains active through Tl2 ® . |

| ' |

2.11 TIMER/COUNTER

Two independent

2.11.1 Timer/Counter Mode Selection

Counter I can be configured in one of four modes: Mode 0) Provides an

prescaler or an

Mode I) Configures counter 1 as a

ing to mode 2 after

Mode 3) When counter I's mode is reprogrammed to mode 3 (from mode 0, I or 2), it disables the incrementing of the counter. This mode is providt;d as an alternative to using the TR I bit (TCON.6) to start and stop counter I.

The serial port receives a pulse each time that counter I overflows. The standard UART modes divide this pulse rate to generate the transmission rate.

Counter 0 can also be configured in one of four modes:

Modes

2.11.2 Configuring the Timer/Counter Input

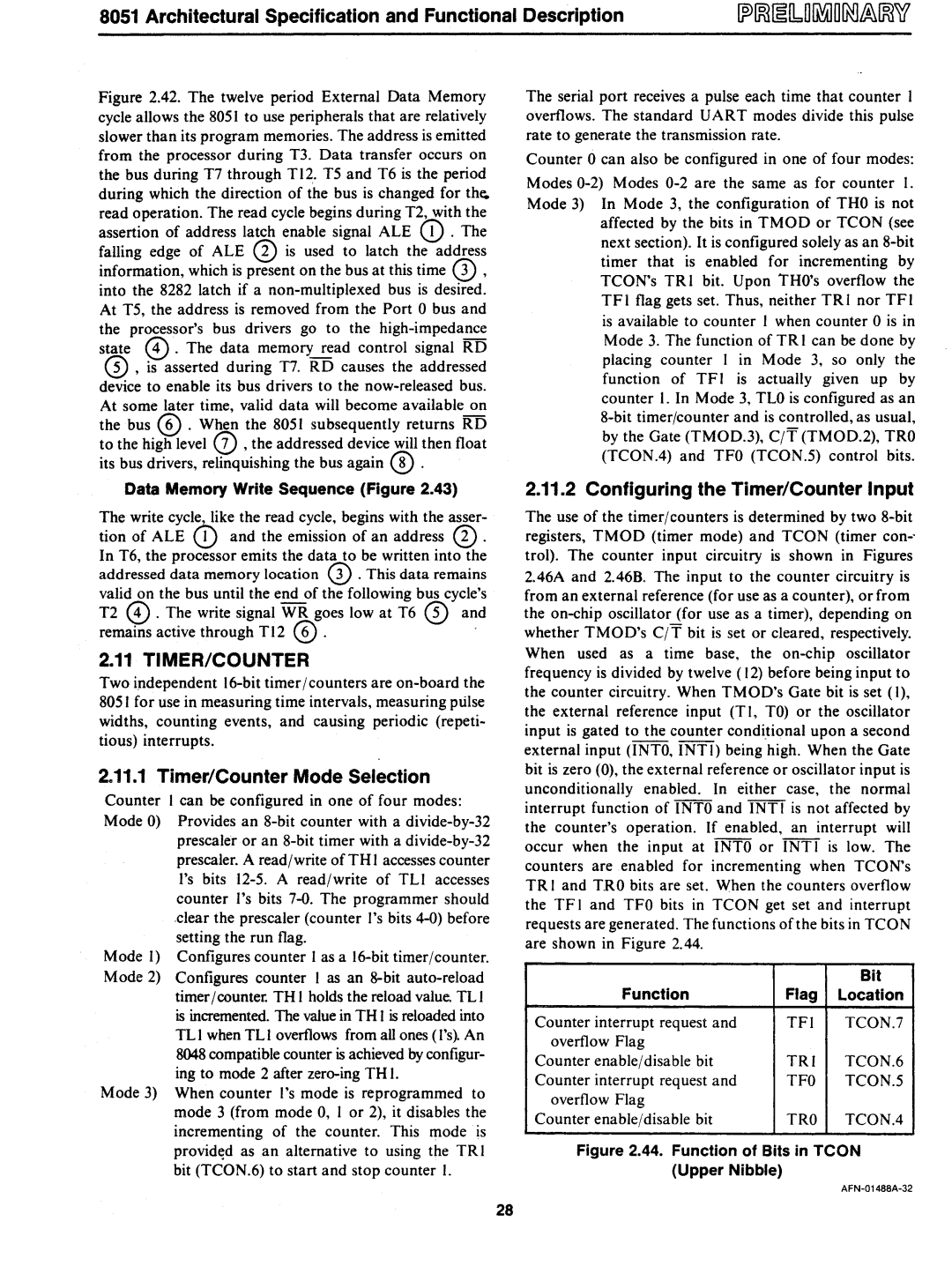

The use of the timer/counters is determined by two

|

| Bit |

Function | Flag | Location |

Counter interrupt request and | TFI | TCON.7 |

overflow Flag |

|

|

Counter enable/disable bit | TRI | TCON.6 |

Counter interrupt request and | TFO | TCON.S |

overflow Flag |

|

|

Counter enable/disable bit | TRO | TCON.4 |

Figure 2.44. Function of Bits in TeON (Upper Nibble)

28