8051 Architectural Specification and Functional Description

•DIRECT Adchuing

-Opet'llnd

RAM (I11III

•REGISTER Addressing

Operand

C

A

R7oRO

DPTR

•

-Opet'llnd

@R1. @RO [I•••• RAM

Note, SFR =Special Funcllon Regia'"

OperaUon

SETB.CLR.CPL

INC. DEC

Operation

SETB.CLR.CPL INC. DEC. DA, CLR. CPL. RL, RLC. RR. RRC.

SWAP INC. DEC INC

Operation

INC. DEC

• | Operation | |

Operand 1 | Operand 2 | |

@R1, @RO[RAM | RAM or SFA | MOV |

@SP [RAM | RAM or SFR | PUSH. POP |

• | Operation | |

Operand 1 | Opera~2 | |

@R1, @RO [RAM | A | MOV |

@R1. @RO [EXT DATA | A | MOYX |

@DPTR[EXT | A | MOYX |

• | Operation | |

Operand 1 | Opera~ 2 | |

@R1, @RO [RAM | PM (immediate) | MOV |

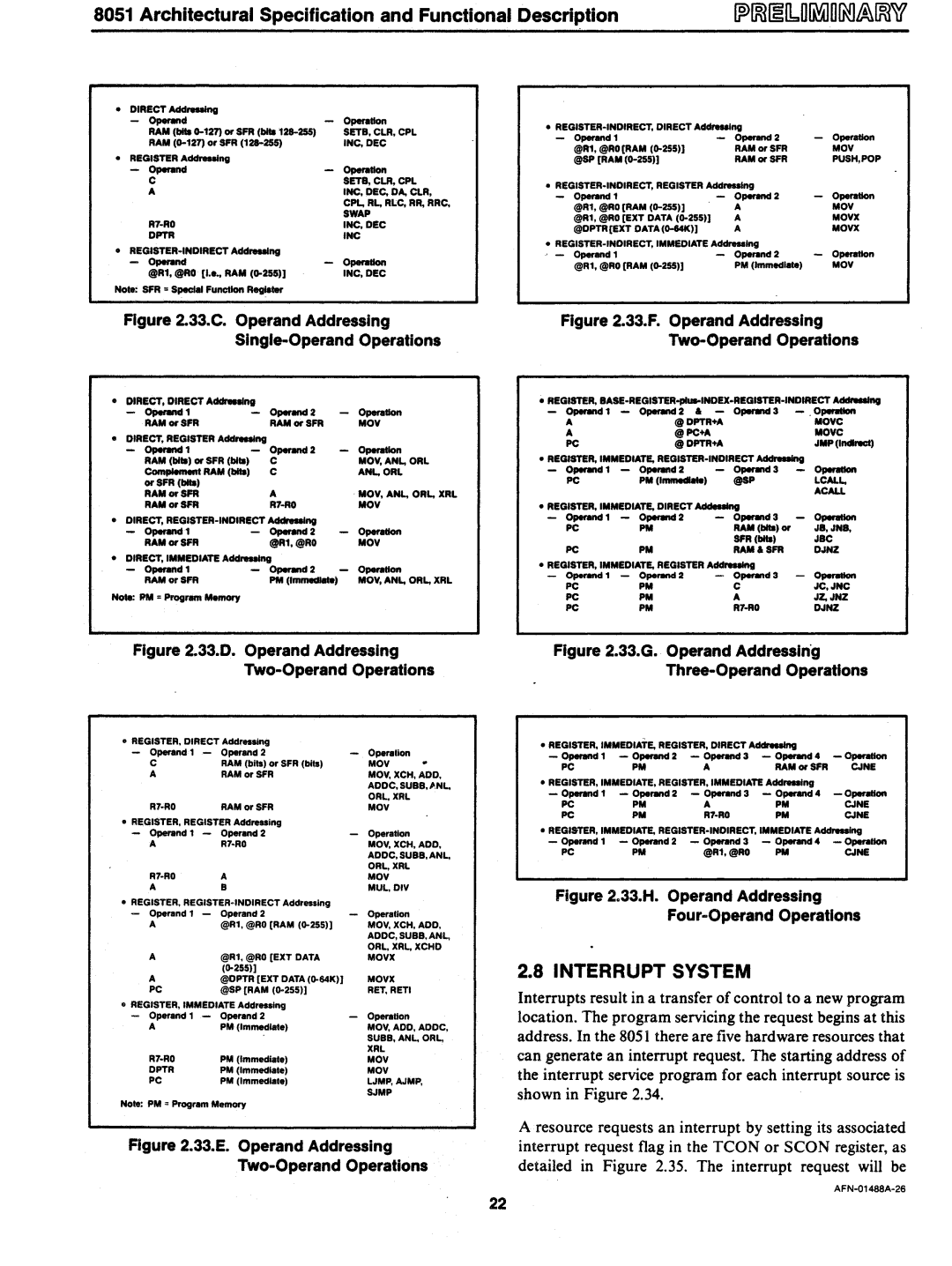

Figure 2.33.C. Operand Addressing Single-Operand Operations

•DIRECT, DIRECT Ad~g

- Opet'llnd1 | Operand 2 | Operation |

RAM or SFA | RAM or SFA | MOV |

•DIRECT. REGISTER Adchuing

Opet'llnd1 | OperMCI 2 | Operation |

RAM (I11III) or SFR (bI") | C | MOV. ANL, ORL |

C~RAM(IIIIII) | C | ANL,ORL |

or SFR (I11III1 |

|

|

RAMorSFA | A | . MOV. ANL, ORL, XRL |

RAM or SFR | MOV |

•DIRECT.

- Operand 1 | - Operand 2 | Operation |

RAM or SFR | @R1. @RD | MOV |

•DIRECT. IMMEDIATE Addressing

- Opmmd1 | OperMCl2 | Operation |

RAM or SFA | PM (ImmedI"') | MOV, ANL, ORL, XRL |

Note: PM = Progr.... M....ory |

|

|

Figure 2.33.F. Operand Addressing Two-Operand Operations

• REGISTER,

Operand 1 | Operand 2 • | - | Operand 3 | . Opsrmlon |

A | @ DPTR+A |

| MOVC | |

A | @PC+A |

|

| MOVC |

PC | @ DPTR+A |

| JMP (IndINcI) | |

• REGISTER. IMMEDIATE, | OperatIon | |||

- Operand 1 - | Operand 2 | - | Operand 3 | |

PC | PM (Immediate) |

| @SP | LCALL, |

|

|

|

| ACALL |

• REGISTER, IMMEDIATE, DIRECT AcIdeuIng |

| |||

Oper~ 1 | Operand 2 |

| Operand 3 | Opsrmlon |

PC | PM |

| RAM (I11III) or | JB,JNB, |

|

|

| SFR(IIIIII) | JBC |

PC | PM |

| RAM • SFA | DJNZ |

• REGISTER, IMMEDIATE, REGISTER Addrasling |

| |||

Operand' | Operand 2 |

| Operand 3 | 0 |

PC | PM |

| C | JC,JNC |

PC | PM |

| A | JZ.JNZ |

PC | PM |

| DJNZ | |

Figure 2.33.D. Operand Addressing | Figure 2.33.G. Operand Addressin'g |

|

|

• REGISTER, DIRECT Addressing

Operand 1 | Operand 2 |

CRAM (bils) or SFR (bl")

ARAMorSFR

RAM or SFR |

• REGISTER, REGISTER Addressing

Operand 1 Operand 2

AR7-RD

R7-RO A

AB

•REGISTER,

Operand 1 | Operand 2 |

A | @R1, @RO [RAM |

A@Rl,@RO [EXT DATA

A | @OPTR [EXT DATA |

PC | @SP[RAM |

• REGISTER, IMMEDIATE Addressing | |

Operand 1 | Operand 2 |

A | PM (Immedlale) |

PM (Immediate) | |

DPTR | PM (Immedlale) |

PC | PM (Immediate) |

Note: PM =Program Memory

Operalion

MOV

MOV, XCH. ADD, ADDC, SUBB,JI.NL,

ORL, XRL MOV

Operation

MOV, XCH, ADD, ADDC, SUBB,ANL,

ORL. XRL MOV MUL,DIV

Operation

MOV, XCH, ADD, ADDC, SUBB, ANL.

ORL, XRL, XCHD MOVX

MOVX

RET, RETI

Operation

MOV, ADD, ADDC, SUBB, ANL, ORL,

XRL

MOV

MOV WMP,AJMP,

SJMP

• REGISTER, IMMEDIATe, REGISTER. DIRECT AcIdnuIng |

| |||

- Operand 1 | - Operand 2 | - Operand 3 | - Operand 4 | - Operation |

PC | PM | A | RAM or SFA | CJNE |

• REGISTER. IMMEDIATE. REGISTER. IMMEDIATE Addressing

-Operand 1 - Operand 2 - Oper~ 3 - Operand 4 - Operation

PC | PM | A | PM | CJNE |

PC | PM | PM | CJNE | |

• REGISTER, IMMEDIATE, | ||||

- Operand 1 | - Operand 2 | - Operand 3 | - Operand 4 | - Operation |

PC | PM | @R1. @RO | PM | CJNE |

Figure 2.33.H. Operand AddreSSing FourmOperand Operations

2.8 INTERRUPT SYSTEM

Interrupts result in a transfer of control to a new program location. The program servicing the request begins at this address. In the 8051 there are five hardware resources that can generate an interrupt request. The starting address of the interrupt service program for each interrupt source is shown in Figure 2.34.

Figure 2.33.E. Operand Addressing Two-Operand Operations

A resource requests an interrupt by setting its associated interrupt request flag in the TCON or SCON register, as detailed in Figure 2.35. The interrupt request will be

22