8051 Architectural Specification and Functional Description

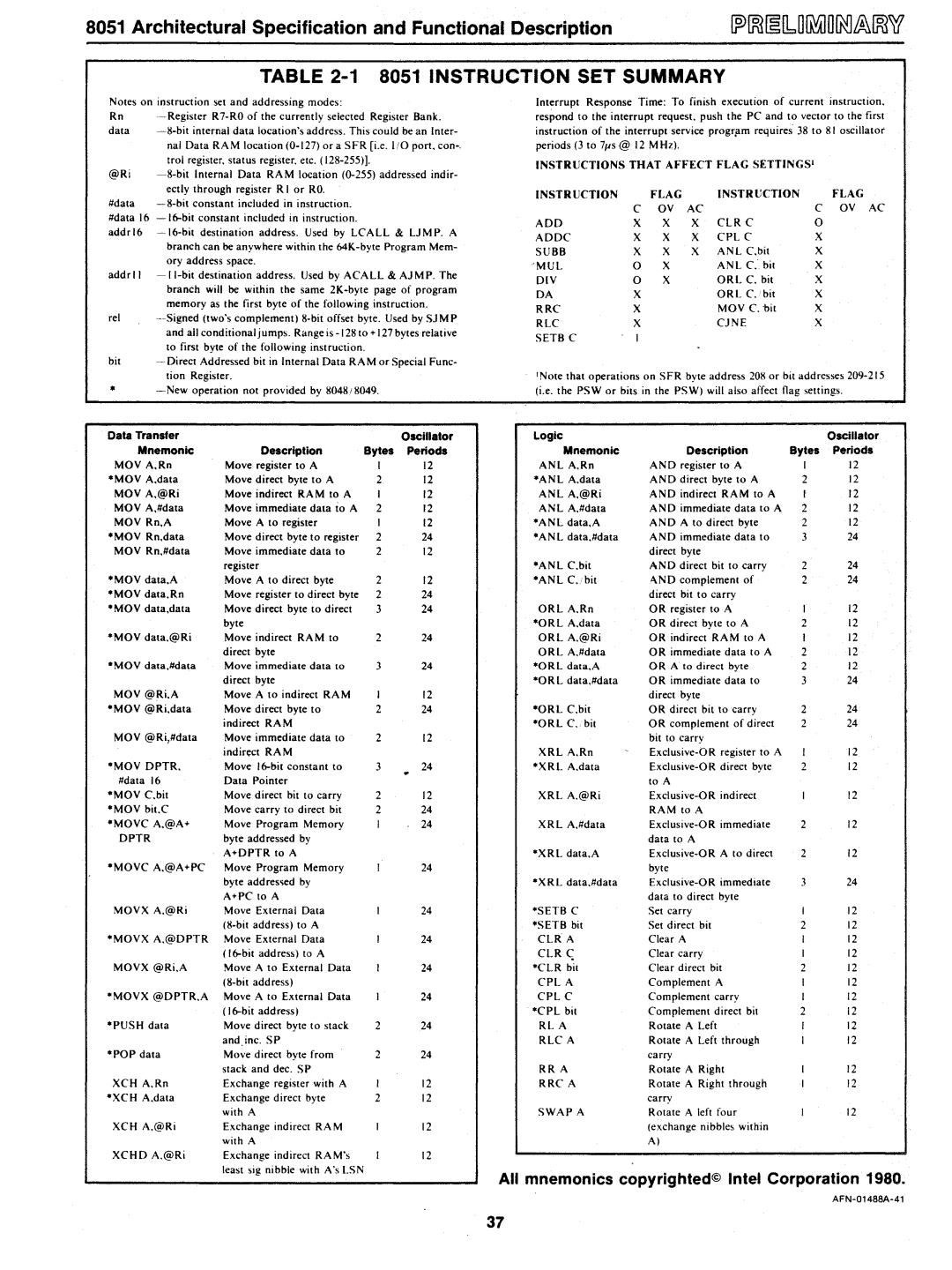

TABLE 2-1 8051 INSTRUCTION SET SUMMARY

Notes on instruction set and addressing modes:

Rn | ·~Register |

data | |

| nal Data RAM location |

| tTOI register. status register. etc. |

@Ri | |

| ectly through register R I or RD. |

Interrupt Response Time: To finish execution of current instruction. respond to the interrupt request. push the PC and to vector to the first instruction of the interrupt service progr.am requires 38 to 81 oscillator periods (3 to 71's @ 12 MHz).

INSTRUCTIONS THAT AFFECT FLAG SETTINGS'

IIdata | |

IIdata | 16 |

addrl6

addrll

| memory as the first byte of the following instruction. |

rei | |

| and all conditionaljumps. Range |

| to first byte of the following instruction. |

bit |

INSTRUCTION FLAG

C OV

ADDX X

ADDCX X

SUBBX X

'MUL0 X

DIV0 X

DAX

RRCX

RLCX SETB C

| INSTRVCTION | FLAG |

AC |

| C OV AC |

X | CLR C | 0 |

X | CPL C | X |

X | ANL C,bit | X |

| ANL C: bit | X |

| ORL C, bit | X |

| ORL C, bit | X |

| MOV C, 'bit | X |

| CJNE | X |

tion Register. |

*- New operation not pTOvided by 8048 i 8049.

Data Tra nafer |

|

| Oscillator |

Mnemonic | Description | Bytes | Periods |

MOV A.Rn | Move· register to A | I | 12 |

"MOV A.data | Move direct byte to A | 2 | 12 |

MOV A.@Ri | Move indirect RAM to A | I | 12 |

MOV A.lldata | Move immediate data io A | 2 | 12 |

MOV Rn.A | Move A to register | I | 12 |

"MOV Rn.data | Move direct byte to register | 2 | 24 |

MOV Rn.lldata | Move immediate data to | 2 | 12 |

| register |

|

|

"MOV data.A | Move A to direct byte | 2 | 12 |

"MOV dala.Rn | Move register 10 direct byte | 2 | 24 |

"MOV data.data | Move direct byte to direct | 3 | 24 |

| byte |

|

|

"MOV data.@Ri | Move indirect RAM to | 2 | 24 |

| direct byte |

|

|

'Note that operations on SFR byte address 20X or bit addresses

Logic |

|

| Oscillator |

Mnemonic | Description | Bytes | Periods |

ANL A.Rn | AND register to A | I | 12 |

"ANL A.data | AND direct byte to A | 2 | 12 |

ANL A.@Ri | AND indirect RAM to A | I | 12 |

ANL A.lldata | AND immediate data to A | 2 | 12 |

"ANL data.A | AND A to direct byte | 2 | 12 |

"ANL data.lldata | AND immediate data to | 3 | 24 |

| direct byte |

|

|

"ANL C,bit | AND direct bit to carry | 2 | 24 |

'ANL C,bit | ... ND complement of | 2 | 24 |

| direct bit to carry |

|

|

ORL A.Rn | OR register to A | I | 12 |

"ORL A.data | OR direct byte to A | 2 | 12 |

ORL A.@Ri | OR indirect RAM to A | I | 12 |

ORL A.lldata | OR immediate data to A | 2 | 12 |

"MOV data.lldata | Move immediate data to |

| direct byte |

MOV@Ri.A | Move A to indirect RAM |

"MOV @Ri.data | Move direct byte to |

| indirect RAM |

MOV @Ri,lIdata | Move immediate data to |

| indirect RAM |

"MOV DPTR. | Move |

IIdata 16 | Data Pointer |

"MOV C,bit | Move direct bit to carry |

"MOV bit.C | Move carry to direct bit |

"MOVC A.@A+ | Move Program Memory |

DPTR | byte addressed by |

| A+DPTR to A |

"MOVC A.@A+PC Move Program Memory | |

| byte addre"ed by |

| A+PC to A |

MOVX A.@Ri | Move External Data |

| |

"MOVX A.@DPTR Move External Data | |

| |

MOVX @Ri.A | Move A to External Data |

| |

·MOVX @DPTR.A Move A to External Data | |

| |

·PUSH data | Move direct byte to staci< |

| and,inc. SP |

'POP data | Move direct byte from |

| staci< and dec. S P |

XCH A.Rn | Exchange register with A |

"XCH A.data | Exchange direct byte |

| with A |

XCH A.@Ri | Exchange indirect RAM |

| with A |

XCHD A.@Ri | Exchange indirect RA M', |

| least sig nibble with A's LSN |

324

I 12

224

212

24

212

224

24

24

24

24

24

24

2 24

224

12

12

12

12

"ORL data.A | OR A to direct byte | 2 | 12 |

'ORL data.lldata | OR immediate data to | 3 | 24 |

| direct byte |

|

|

"ORL C,bit | OR direct bit to carry |

| 24 |

"ORL C, bit | OR complement of direct |

| 24 |

| bit to carry |

|

|

XRL A.Rn |

| 12 | |

"XRL A.data |

| 12 | |

| to A |

|

|

XRL A.@Ri |

| 12 | |

| RAM to A |

|

|

XRL A.lldata |

| 12 | |

| data to A |

|

|

'XRL data.A | 2 | 12 | |

| byte |

|

|

"XRL data.lldata |

| 24 | |

| data to direct byte |

|

|

·SETB C | Set carry | 1 | 12 |

"SETB bit | Set direct bit | 2 | 12 |

CLR A | Clear A |

| 12 |

CLR c.: | Clear carry |

| 12 |

·CLR bit | Clear direct bit | 2 | 12 |

CPL A | Complement A |

| 12 |

CPL C | Complement carry |

| 12 |

"CPL bit | Complement direct bit |

| 12 |

RL A | Rotate A Left |

| 12 |

RLC A | Rotate A Left through |

| 12 |

| carry |

|

|

RR A | Rotate A Right |

| 12 |

RRC A | Rotate A Right through |

| 12 |

| carry |

|

|

SWAP A | Rotate A left four |

| 12 |

| (exchange nibbles within |

|

|

| A) |

|

|

All mnemonics copyrighted© Intel Corporation 1980.

37