8051 Architectural Specification and Functional Description

| PULSE TO |

COUNTER 1 | SERIAL PORT |

MODE 0: |

|

| |

MODE 1: |

|

MODE 2: 8·BITAUTO·RELOADTIC |

|

MODE 3: PREVENTS INCREMENTING |

|

OF TIC |

|

T1

COUNTER 0

XTAL1

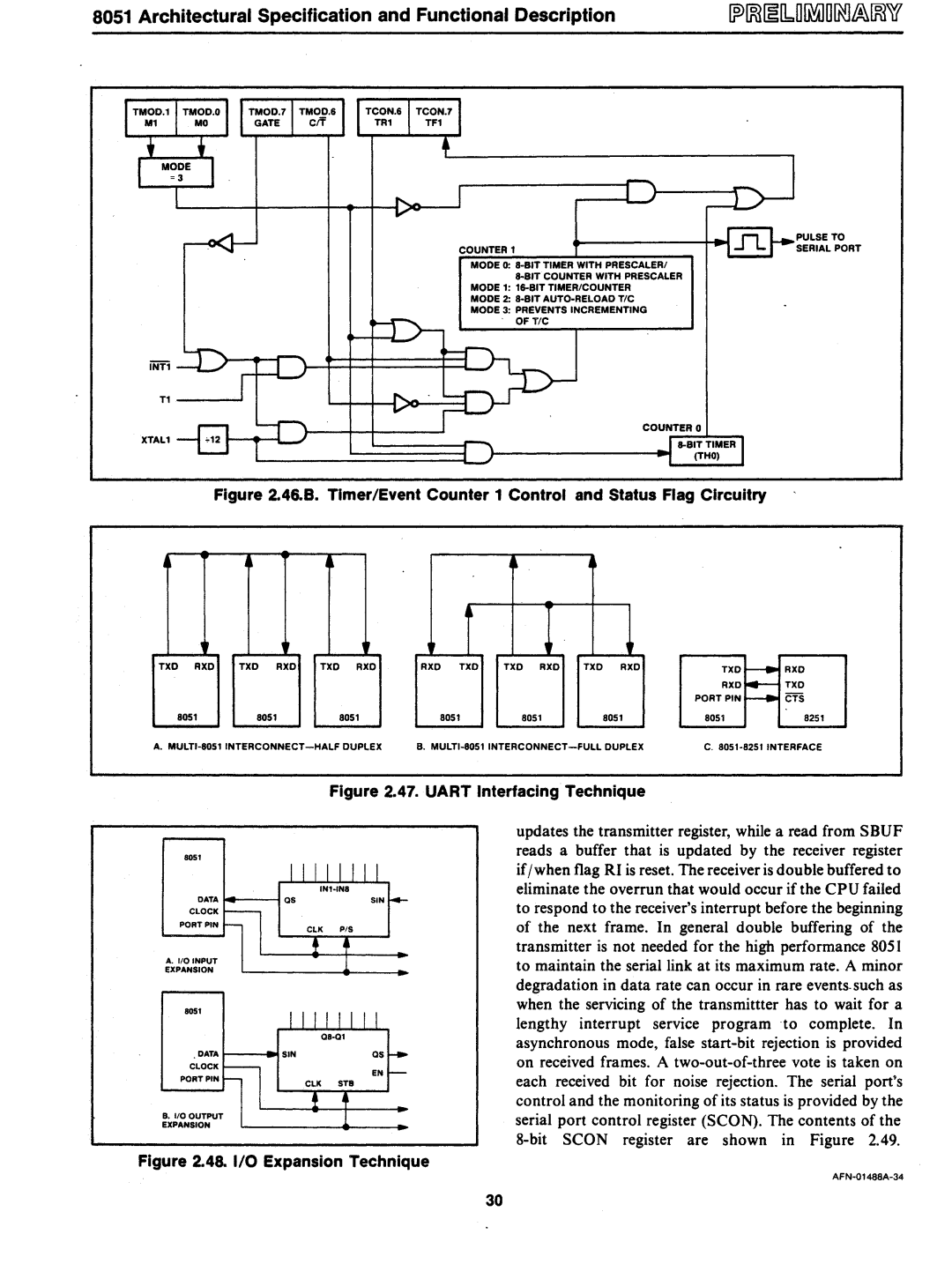

Figure 2.46.8. Timer/Event Counter 1 Control and Status Flag Circuitry

~

~

TXD RXD | TXD RXD | TXD RXD | RXD TXD | TXD RXD | TXD RXD | TXD |

|

|

|

|

|

| RXD |

|

|

|

|

|

| PORT PIN |

8051 | 8051 | 8051 | 8051 | 8051 | 8051 | 8051 |

~

RXD

TXD

ffi

8251

A. MULTI·8051 | B. MULTI·8051 | C. 8051·8251 INTERFACE |

Figure 2.47. UART Interfacing Technique

8051 |

|

DATA | SIN |

CLOCK |

|

PORT PIN |

|

A.IiOINPUT

EXPANSION

8051

. OATAt

CLOCK

EN

PORT PIN

B.IiOOUTPUT

EXPANSION

updates the transmitter register, while a read from SBUF reads a buffer that is updated by the receiver register if/ when flag RI is reset. The receiver is double buffered to eliminate the overrun that would occur ifthe CPU failed to respond to the receiver's interrupt before the beginning of the next frame. In general double buffering of the transmitter is not needed for the high performance 8051 to maintain the serial link at its maximum rate. A minor degradation in data rate can occur in rare events. such as when the servicing of the transmittter has to wait for a lengthy interrupt service program to complete. In asynchronous mode, false

Figure 2.48. I/O Expansion Technique

AFN·01488A·34

30