8051 Architectural Specification and Functional Description

1.0 ABSTRACT

The 8031, 8051, and 8751 are the latest additions to Inters line of single-chip microcomputers. The CPU architec- ture and on-chip peripheral functions of the 8051 are described in this document. A user familiar with the MCS-48 family should be able to evaluate and design-in the 8051 using the information included herein.

A detailed description of the hardware required to expand the 8051 with more program memory, data memory, I/O, specialized peripherals and into multi- processor configurations is described in the 8051 Family User's Manual.

Now, thanks to the density of HMOS, technology has once again permitted the birth of a microcomputer with performance to leap into new product areas. The 8051 achieves a lOX function/speed improvement over the 8048 by packing 60,000 transistors onto a die 230 mils square.

The 8051 family addresses the high-end of the single-chip computer market. It is the highest performance micfo- computer family in the world and out-performs all micro- processors and microcomputers in control oriented applications. It offers an upward compatible growth path for 8048 users with ten times the power of the 8048 as shown in Table 1.1.

1.1INTEL'SCOMPLETE LINE OF SINGLE-CHIP MICROCOMPUTERS

In 1976 Intel introduced the 8748 microcomputer. This marked the first time in history that technology permitted a complete 8-bit computer to be fabricated on a single silicon die. This single chip can control a limitless variety of products ranging from appliances to automobiles to computer terminals.

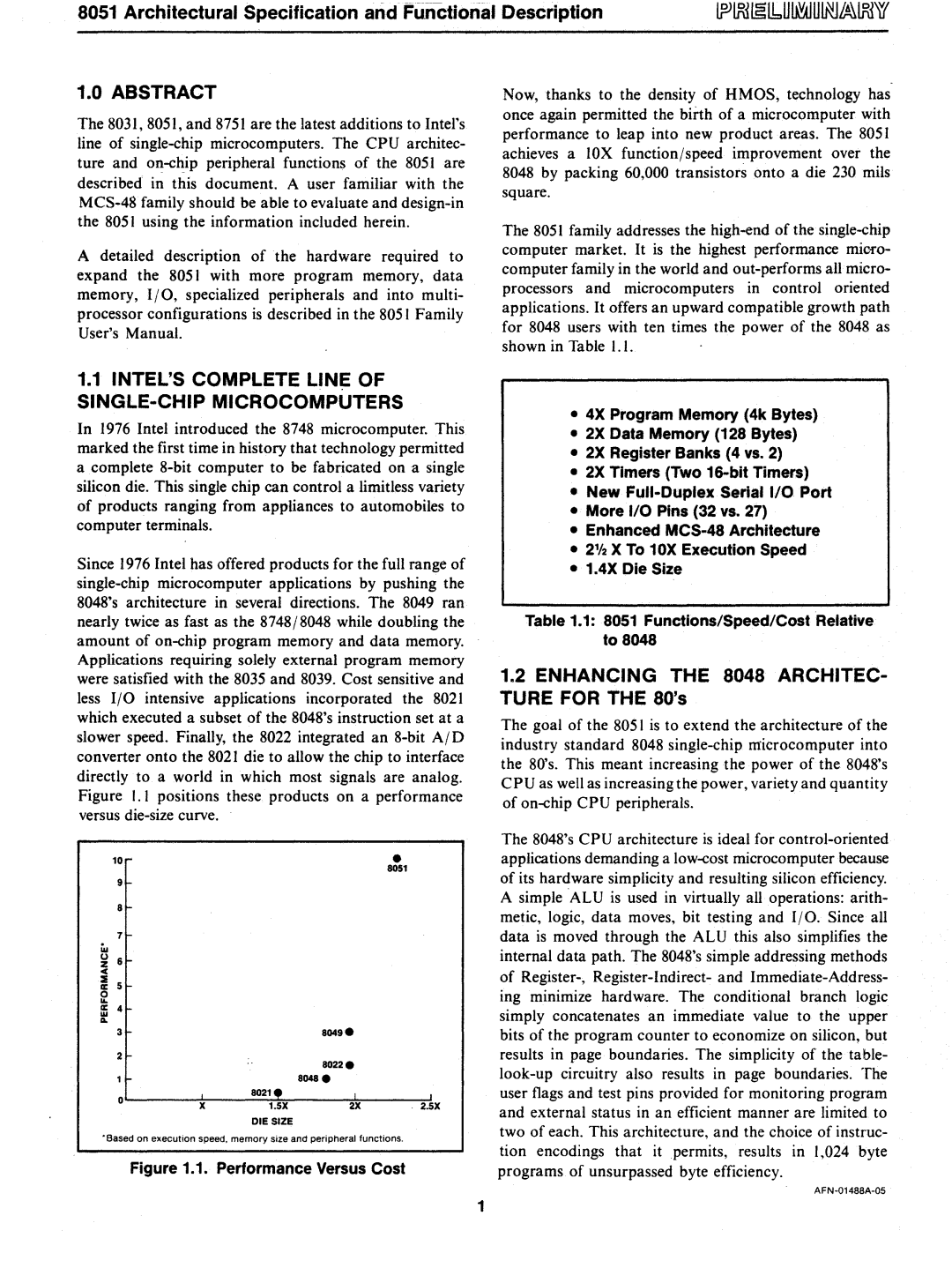

Since 1976 Intel has offered products for the full range of single-chip microcomputer applications by pushing the 8048's architecture in several directions. The 8049 ran nearly twice as fast as the 8748/8048 while doubling the amount of on-chip program memory and data memory. Applications requiring solely external program memory were satisfied with the 8035 and 8039. Cost sensitive and less I/O intensive applications incorporated the 8021 which executed a subset of the 8048's instruction set at a slower speed. Finally, the 8022 integrated an 8-bit A/D converter onto the 8021 die to allow the chip to interface directly to a world in which most signals are analog. Figure I. I positions these products on a performance versus die-size curve.

| 10 | | | | • |

| | | | | 8051 |

| 9 | | | | |

| 8 | | | | |

iu | 7 | | | | |

| | | | |

il | 6 | | | | |

c | | | | | |

o~ | 5 | | | | |

... | | | | | |

ffi | 4 | | | | |

... | 3 | | | | |

| | | | |

| 2 | | | 8022. | |

| | | | |

| | | | 8048 • | |

| 0~ | *X | 8021.------ | ~2~X------ | .~2.5X |

| ~~1~.5~X |

DIE SIZE

-Based on execution speed, memory size and peripheral functions.

Figure 1.1. Performance Versus Cost

1

•4X Program Memory (4k Bytes)

•2X Data Memory (128 Bytes)

•2X Register Banks (4 vs. 2)

•2X Timers (Two 16-bit Timers)

•New Full-Duplex Serial I/O Port

•More I/O Pins (32 vs. 27)

•Enhanced MCS-48 Architecture

•21/2 X To 10X Execution Speed

•1.4X Die Size

Table 1.1: 8051 Functions/Speed/Cost Relative to 8048

1.2ENHANCING THE 8048 ARCHITEC- TURE FOR THE 80's

The goal of the 8051 is to extend the architecture of the industry standard 8048 single-chip microcomputer into the 80's. This meant increasing the power of the 8048's CPU as well as increasing the power, variety and quantity of on-chip CPU peripherals.

The 8048's CPU architecture is ideal for control-oriented applications demanding a low-cost microcomputer because of its hardware simplicity and resulting silicon efficiency. A simpleALU is used in virtually all operations: arith- metic, logic, data moves, bit testing and I/O. Since all data is moved through the ALU this also simplifies the internal data path. The 8048's simple addressing methods of Register-, Register-Indirect- and Immediate-Address- ing minimize hardware. The conditional branch logic simply concatenates an immediate value to the upper bits of the program counter to economize on silicon, but results in page boundaries. The simplicity of the table- look-up circuitry also results in page boundaries. The user flags and test pins provided for monitoring program and external status in an efficient manner are limited to two of each. This architecture, and the choice of instruc- tion encodings that it permits, results In 1,024 byte programs of unsurpassed byte efficiency.

AFN-01488A-05