8051 Architectural Specification and Functional Description

REG~~TER 141...

'SPIs

Figure 2.30. Return Operation

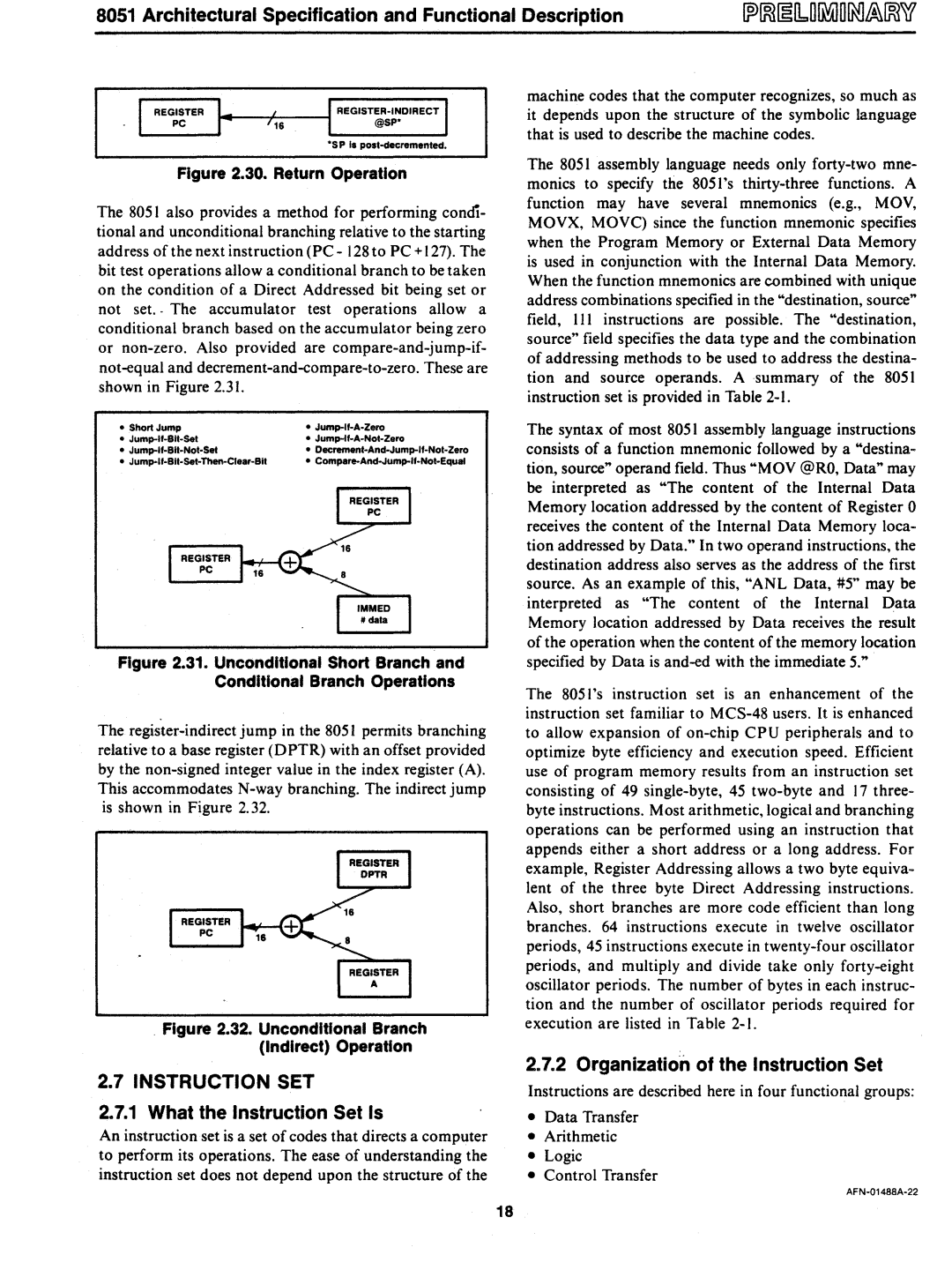

The 805 I also provides a method for performing condi- tional and unconditional branching relative to the starting address of the next instruction (PC - 128 to PC + 127). The bit test operations allow a conditional branch to be taken on the condition of a Direct Addressed bit being set or not set.· The accumulator test operations allow a conditional branch based on the accumulator being zero or

• | Short Jump | • | |

• | • | ||

• | • | ||

• | • | ||

Figure 2.31. Unconditional Short Branch and

Conditional Branch Operations

The

. Figure 2.32. Unconditional Branch (Indirect) Operation

machine codes that the computer recognizes, so much as it depends upon the structure of the symbolic language that is used to describe the machine codes.

The 8051 assembly language needs only

The syntax of most 805 I assembly language instructions consists of a function mnemonic followed by a "destina- tion, source" operand field. Thus "MOV @RO, Data" may be interpreted as "The content of the Internal Data Memory location addressed by the content of Register 0 receives the content of the Internal Data Memory loca- tion addressed by Data." In two operand instructions, the destination address also serves as the address of the first source. As an example of this, "ANL Data, #5" may be interpreted as "The content of the Internal Data Memory location addressed by Data receives the result of the operation when the content of the memory location specified by Data is

The 8051 's instruction set is an enhancement of the instruction set familiar to

2.7INSTRUCTION SeT

2.7.1What the Instruction Set Is

An instruction set is a set of codes that directs a computer to perform its operations. The ease of understanding the instruction set does not depend upon the structure of the

2.7.2Organization of the Instruction Set

Instructions are described here in four functional groups:

•Data Transfer

•Arithmetic

•Logic

•Control Transfer

18