8051

Microcomputer

Architectural Specification

and

Functional Description

©Intel Corporation 1980. All rights reserved.

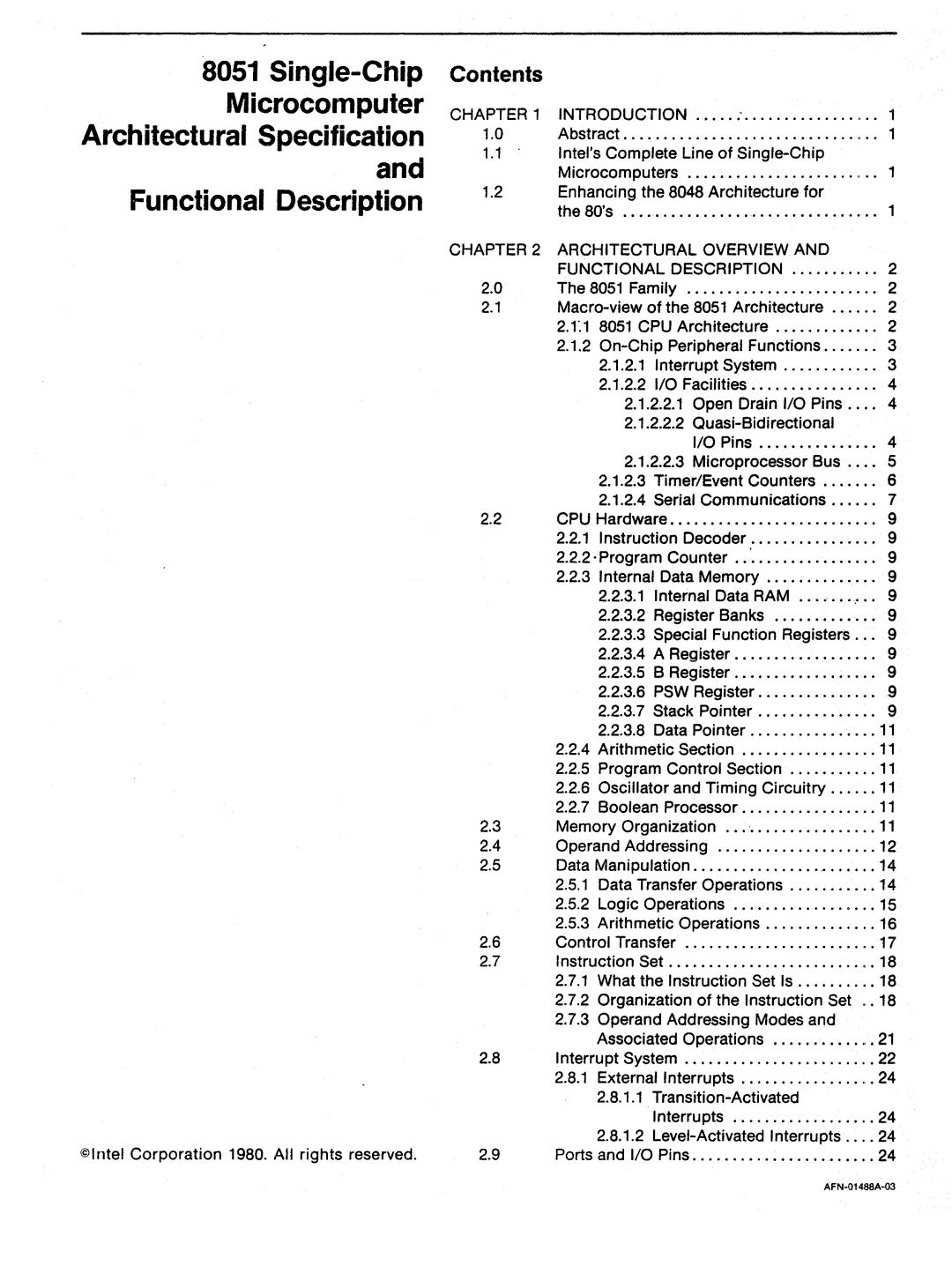

Contents

CHAPTER 1 | INTRODUCTION | 1 | |

1.0 | Abstract | . . . . . . . . . . . . . . . .. .. | 1 |

1.1Intel'sComplete Line of

Microcomputers | 1 |

1.2Enhancing the 8048 Architecture for

| the 80's |

| 1 | ||

CHAPTER 2 ARCHITECTURAL OVERVIEW AND |

| ||||

| FUNCTIONAL DESCRIPTION | 2 | |||

2.0 | The 8051 Family | 2 | |||

2.1 | 2 | ||||

| 2.1:1 8051 CPU Architecture | 2 | |||

| 2.1.2 | 3 | |||

|

| 2.1.2.1 | Interrupt System | 3 | |

|

| 2.1.2.2 | I/O Facilities | 4 | |

|

| 2.1.2.2.1 | Open Drain I/O Pins. . .. | 4 | |

|

| 2.1.2.2.2 |

| ||

|

|

|

| I/O Pins | 4 |

|

| 2.1.2.2.3 Microprocessor Bus .. .. | 5 | ||

|

| 2.1.2.3 Timer/Event Counters | 6 | ||

|

| 2.1.2.4 Serial Communications | 7 | ||

2.2 | CPU Hardware. .. | . .. . .. .. .. . .. .. .. . .. ... | 9 | ||

| 2.2.1 | Instruction Decoder | 9 | ||

| 2.2.2'Program Counter | 9 | |||

| 2.2.3 | Internal Data Memory | 9 | ||

|

| 2.2.3.1 | Internal Data RAM | 9 | |

|

| 2.2.3.2 | Register Banks .• | 9 | |

|

| 2.2.3.3 | Special Function Registers ... | 9 | |

|

| 2.2.3.4 A Register | 9 | ||

|

| 2.2.3.5 | B Register | 9 | |

|

| 2.2.3.6 PSW Register | 9 | ||

|

| 2.2.3.7 | Stack Pointer | 9 | |

|

| 2.2.3.8 | Data Pointer | 11 | |

| 2.2.4 Arithmetic Section | 11 | |||

| 2.2.5 | Program Control Section | 11 | ||

| 2.2.6 | Oscillator and Timing Circuitry | 11 | ||

| 2.2.7 | Boolean Processor | 11 | ||

2.3 | Memory Organization | 11 | |||

2.4 | Operand Addressing | 12 | |||

2.5 | Data Manipulation | ............... " | 14 | ||

| 2.5.1 | Data Transfer Operations | 14 | ||

| 2.5.2 | logic Operations | 15 | ||

| 2.5.3 | Arithmetic Operations | 16 | ||

2.6 | Control Transfer | 17 | |||

2.7 | Instruction Set | 18 | |||

| 2.7.1 | What the Instruction Set Is | 18 | ||

| 2.7.2 Organization of the Instruction Set ". 18 | ||||

| 2.7.3 Operand Addressing Modes and |

| |||

|

| Associated Operations | 21 | ||

2.8 | Interrupt System | 22 | |||

| 2.8.1 | External Interrupts | 24 | ||

2.8.1.1

Interrupts .................. 24

2.8.1.2

2.9 | Ports and I/O Pins | 24 |