8051 Architectural Specification and Functional Description

T12

OSC

ALE

PORT 2

PORTO

ALE

FLOAT

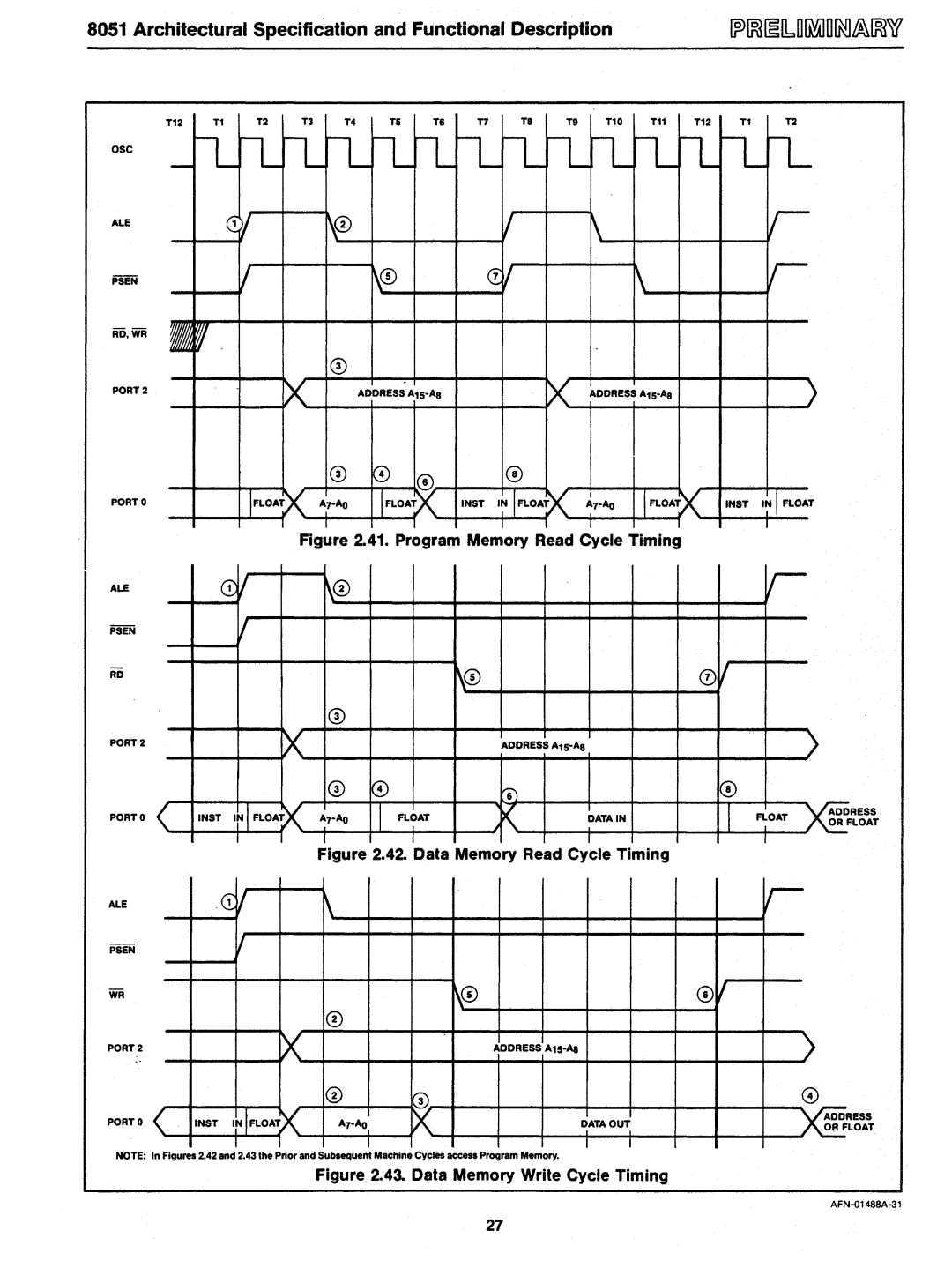

| Figure 2.41. Program Memory Read Cycle Timing |

|

CDV | \0 | I |

V |

|

|

RD | ~0 |

|

0

PORT 2 |

| X |

|

| ADDRESS |

|

|

|

|

|

| ||

| INST Irl FLOAT | 0 | 0 | (6) |

| |

PORTO | I FLOAT | >( | DATA IN | |||

| I | I | I | I |

| I |

Figure 2.42. Data Memory Read Cycle Timing

ALE |

| G::V |

| \ |

|

|

|

|

|

|

|

|

|

| |

|

| II |

|

|

|

|

|

|

|

|

| ® | \0 |

|

|

|

|

| X |

|

|

| |

PORT 2 |

|

|

| ADDRESS |

|

| |

|

|

|

|

|

| ||

|

| IN IFLOAT | 0 | ~ |

|

| |

PORTO | INST | D< | DATA OUT | ||||

|

| ||||||

|

| I | I | I |

| I | I |

NOTE: In Figures 2.42 and 2.43 the Prior and Subsequent Machine Cycles access Program Memory. |

|

| |||||

CD 1/

®

I ADDRESS

FLOAT ORFLOAT

I

II

@II

0

ADDRESS

OR FLOAT

Figure 2.43. Data Memory Write Cycle Timing

27