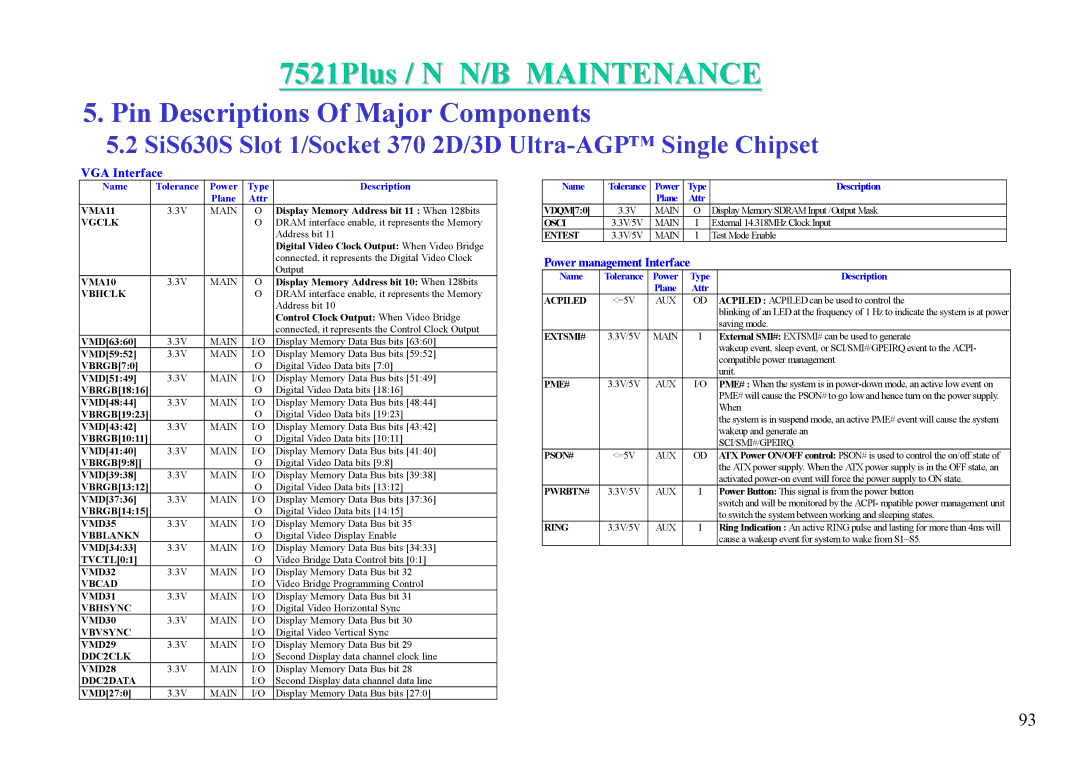

7521Plus / N N/B MAINTENANCE

5.Pin Descriptions Of Major Components

5.2SiS630S Slot 1/Socket 370 2D/3D Ultra-AGP™ Single Chipset

VGA Interface

Name | Tolerance | Power | Type | Description |

|

| Plane | Attr |

|

VMA11 | 3.3V | MAIN | O | Display Memory Address bit 11 : When 128bits |

VGCLK |

|

| O | DRAM interface enable, it represents the Memory |

|

|

|

| Address bit 11 |

|

|

|

| Digital Video Clock Output: When Video Bridge |

|

|

|

| connected, it represents the Digital Video Clock |

|

|

|

| Output |

VMA10 | 3.3V | MAIN | O | Display Memory Address bit 10: When 128bits |

VBHCLK |

|

| O | DRAM interface enable, it represents the Memory |

|

|

|

| Address bit 10 |

|

|

|

| Control Clock Output: When Video Bridge |

|

|

|

| connected, it represents the Control Clock Output |

VMD[63:60] | 3.3V | MAIN | I/O | Display Memory Data Bus bits [63:60] |

VMD[59:52] | 3.3V | MAIN | I/O | Display Memory Data Bus bits [59:52] |

VBRGB[7:0] |

|

| O | Digital Video Data bits [7:0] |

VMD[51:49] | 3.3V | MAIN | I/O | Display Memory Data Bus bits [51:49] |

VBRGB[18:16] |

|

| O | Digital Video Data bits [18:16] |

VMD[48:44] | 3.3V | MAIN | I/O | Display Memory Data Bus bits [48:44] |

VBRGB[19:23] |

|

| O | Digital Video Data bits [19:23] |

VMD[43:42] | 3.3V | MAIN | I/O | Display Memory Data Bus bits [43:42] |

VBRGB[10:11] |

|

| O | Digital Video Data bits [10:11] |

VMD[41:40] | 3.3V | MAIN | I/O | Display Memory Data Bus bits [41:40] |

VBRGB[9:8]] |

|

| O | Digital Video Data bits [9:8] |

VMD[39:38] | 3.3V | MAIN | I/O | Display Memory Data Bus bits [39:38] |

VBRGB[13:12] |

|

| O | Digital Video Data bits [13:12] |

VMD[37:36] | 3.3V | MAIN | I/O | Display Memory Data Bus bits [37:36] |

VBRGB[14:15] |

|

| O | Digital Video Data bits [14:15] |

VMD35 | 3.3V | MAIN | I/O | Display Memory Data Bus bit 35 |

VBBLANKN |

|

| O | Digital Video Display Enable |

VMD[34:33] | 3.3V | MAIN | I/O | Display Memory Data Bus bits [34:33] |

TVCTL[0:1] |

|

| O | Video Bridge Data Control bits [0:1] |

VMD32 | 3.3V | MAIN | I/O | Display Memory Data Bus bit 32 |

VBCAD |

|

| I/O | Video Bridge Programming Control |

VMD31 | 3.3V | MAIN | I/O | Display Memory Data Bus bit 31 |

VBHSYNC |

|

| I/O | Digital Video Horizontal Sync |

VMD30 | 3.3V | MAIN | I/O | Display Memory Data Bus bit 30 |

VBVSYNC |

|

| I/O | Digital Video Vertical Sync |

VMD29 | 3.3V | MAIN | I/O | Display Memory Data Bus bit 29 |

DDC2CLK |

|

| I/O | Second Display data channel clock line |

VMD28 | 3.3V | MAIN | I/O | Display Memory Data Bus bit 28 |

DDC2DATA |

|

| I/O | Second Display data channel data line |

VMD[27:0] | 3.3V | MAIN | I/O | Display Memory Data Bus bits [27:0] |

Name | Tolerance | Power | Type | Description |

|

| Plane | Attr |

|

VDQM[7:0] | 3.3V | MAIN | O | Display Memory SDRAMInput /Output Mask |

OSCI | 3.3V/5V | MAIN | I | External 14.318MHz Clock Input |

ENTEST | 3.3V/5V | MAIN | I | Test Mode Enable |

Power management Interface

Name | Tolerance | Power | Type | Description |

|

| Plane | Attr |

|

ACPILED | <=5V | AUX | OD | ACPILED : ACPILED can be used to control the |

|

|

|

| blinking of an LED at the frequency of 1 Hz to indicate the system is at power |

|

|

|

| saving mode. |

EXTSMI# | 3.3V/5V | MAIN | I | External SMI#: EXTSMI# can be used to generate |

|

|

|

| wakeup event, sleep event, or SCI/SMI#/GPEIRQ event to the ACPI- |

|

|

|

| compatible power management |

|

|

|

| unit. |

PME# | 3.3V/5V | AUX | I/O | PME# : When the system is in |

|

|

|

| PME# will cause the PSON# to go low and hence turn on the power supply. |

|

|

|

| When |

|

|

|

| the system is in suspend mode, an active PME# event will cause the system |

|

|

|

| wakeup and generate an |

|

|

|

| SCI/SMI#/GPEIRQ. |

PSON# | <=5V | AUX | OD | ATX Power ON/OFF control: PSON# is used to control the on/off state of |

|

|

|

| the ATX power supply. When the ATX power supply is in the OFF state, an |

|

|

|

| activated |

PWRBTN# | 3.3V/5V | AUX | I | Power Button: This signal is from the power button |

|

|

|

| switch and will be monitored by the ACPI- mpatible power management unit |

|

|

|

| to switch the system between working and sleeping states. |

RING | 3.3V/5V | AUX | I | Ring Indication : An active RING pulse and lasting for more than 4ms will |

|

|

|

| cause a wakeup event for system to wake from S1~S5. |

93