ANY-FREQUENCY Precision Clocks

Si53xx-RM

Table of Contents

Output Clock Drivers

Si5375 Free Run Mode

High-Speed I/O

Si53xx-RM

List of Figures

Differential Output Example Requiring Attenuation 108

Si53xx-RM

List of Tables

Si53xx-RM

Any-Frequency Precision Clock Product Family Overview

Si53xx-RM

Product Selection Guide

PLL

Product Selection Guide Si5322/25/65/67

Device

Precision Clock Multipliers Wideband

Narrowband vs. Wideband Overview

Any-Frequency Clock Family Members

Si5316

Si5319

Dspll

Si5322 Low Jitter Clock Multiplier Block Diagram

Si5322

Si5323 Jitter Attenuating Clock Multiplier Block Diagram

Si5323

Si5324 Clock Multiplier and Jitter Attenuator Block Diagram

Si5324

Si5325 Low Jitter Clock Multiplier Block Diagram

Si5325

Si5326 Clock Multiplier and Jitter Attenuator Block Diagram

Si5326

Si5327 Clock Multiplier and Jitter Attenuator Block Diagram

Si5327

Si5365 Low Jitter Clock Multiplier Block Diagram

Si5365

Si5366 Jitter Attenuating Clock Multiplier Block Diagram

10. Si5366

Si5367 Clock Multiplier Block Diagram

11. Si5367

Si5368 Clock Multiplier and Jitter Attenuator Block Diagram

12. Si5368

13. Si5369

14. Si5374/75 Compared to Si5324/19

Si5374 Functional Block Diagram

15. Si5374

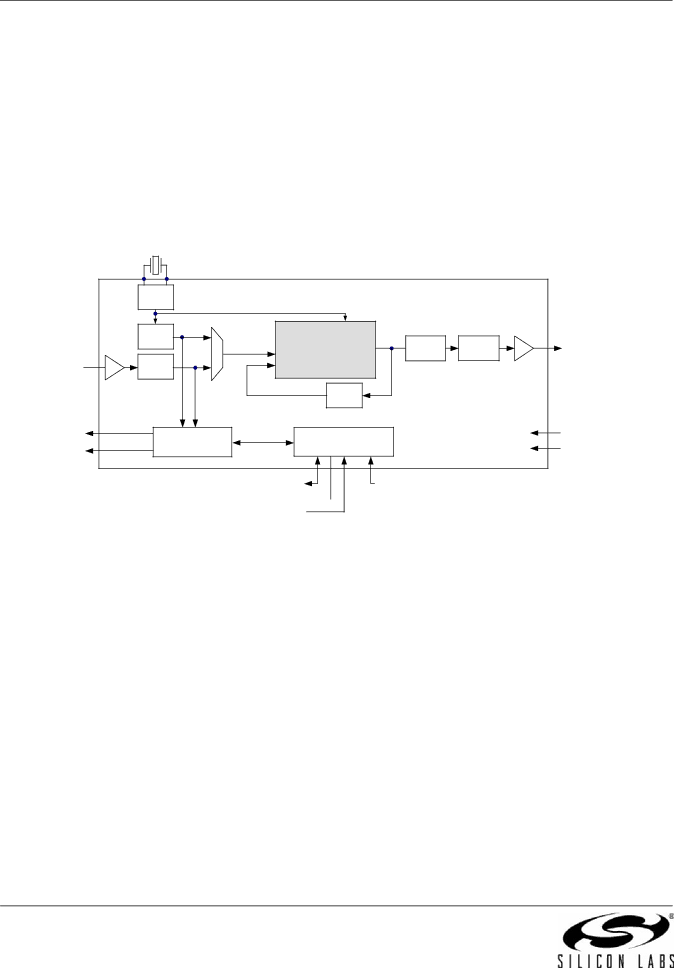

Si5375 Functional Block Diagram

16. Si5375

Recommended Operating Conditions1

Device Specifications

Parameter Symbol Test Condition

Min Typ Max Unit

DC Characteristics

CKINn Input Pins

Lvpecl 100 Ω

Level Lvcmos Input Pins

Level Input Pins

Lvcmos Output Pins

RST

SPI Specifications Si5324, Si5325, Si5367, and Si5368

Parameter Symbol Test Conditions Min Typ Max Unit

Differential Reference Clock Input Pins XA/XB

SDO

Frame Synchronization Timing

AC Characteristics-All Devices

Min Typ Max Units

Lvcmos Pins

Device Skew

PLL Performance

Ckopn

Jitter Generation Si5316, Si5324, Si5366, Si5368

Jitter Generation Si5322, Si5325, Si5365, Si5367

Thermal Characteristics

Parameter Symbol Test Condition Devices Value Unit

Any-Frequency Precision Clock Dspll Block Diagram

Dspll All Devices

Clock Multiplication

Clock Multiplication Circuit

PLL Performance

Jitter Generation

Jitter Transfer

Jitter Tolerance Mask/Template

Jitter Tolerance

Pin Control Parts Si5316, Si5322, Si5323, Si5365, Si5366

Si5316, Si5322, Si5323, Si5365 and Si5366 Key Features

Frequency Settings

Clock Multiplication Si5316, Si5322, Si5323, Si5365, Si5366

CKnDIV N3n Input Divider

Input Divider Settings

Si5316 Bandwidth Values

FRQSEL10 Nominal Frequency Values MHz BW10

Fsout MHz

Sonet Clock Multiplication Settings FRQTBL=L

Clock Multiplication Si5322, Si5323, Si5365, Si5366

Ckconf =

FIN MHz Mult Factor

All Devices Si5366 Only FOUT MHz

Mllm

Hlll

Hhlh

Datacom Clock Multiplication Settings Frqtbl = M, Ckconf =

Setting

MHz Mult Factor OUT* MHz

125 10/8 x 66/64 161.13

173.37 X 64/66 x 237/255 125

Hhhl

Sonet to Datacom Clock Multiplication Settings

FIN MHz Mult Factor FOUT* MHz

62.500 125

155.520 15625/15552 156.25

Lock Detect Si5322 and Si5365

Clock Output Divider Control DIV34

CKOUT3 and CKOUT4 Si5365 and Si5366

Input-to-Output Skew Si5322 and Si5365

PLL Self-Calibration

Si5316, Si5322, and Si5323 Pins and Reset

Si5365 and Si5366 Pins and Reset

Pin Control Input Clock Control

Manual Input Clock Selection Si5365, Si5366, Autosel = L

Input Clock Priority for Auto Switching Si5322, Si5323

Clock Active Indicators Autosel = M or H Si5322 and Si5323

Clock Active Indicators Autosel = M or H Si5365 and Si5367

Automatic/Manual Clock Selection

Input Clock Priority for Auto Switching Si5365, Si5366

Hitless Switching with Phase Build-Out Si5323, Si5366

Frame Synchronization Si5366

Recovery from Digital Hold Si5316, Si5323, Si5366

Digital Hold/VCO Freeze

Narrowband Digital Hold Si5316, Si5323, Si5366

Fsync Realignment Si5366

Output Phase Adjust Si5323, Si5366

Using Fsout as a Fifth Output Clock Si5366

Including Fsync Inputs in Clock Selection Si5366

Fsout Disable Control Dblfs

Output Signal Format Selection Sfout

Output Clock Drivers

PLL Bypass Mode

Alarms

DSBL2/BYPASS Pin Settings

Alarm Output Logic Equations

Frequency Offset Control Fosctl

Device Reset

DSPLLsim Configuration Software

Lock Detect Retrigger Time

Wideband PLL Divider Settings Si5325, Si5367

Loop Bandwidth Si5325, Si5367

Lock Detect Si5325, Si5367

Input to Output Skew Si5325, Si5367

Signal Frequency Limits

Dividers and Limits

Loop Bandwidth Si5319, Si5326, Si5368, Si5375

Low Loop Bandwidth Si5324, Si5327, Si5369, Si5374

Initiating Internal Self-Calibration

Ckoutalwayson and Sqical Truth Table

Input Clock Configurations Si5367 and Si5368

Input Clock Control

Register Bits

Manual Input Clock Selection Si5367, Si5368, Si5369

Active Input Clock

CKIN1,2,3,4 inputs CKIN1,3 & CKIN2,4 clock/FSYNC pairs

Manual Input Clock Selection Si5324, Si5325, Si5326, Si5374

Ckselreg or CS pin Active Input Clock

Input Clock Priority for Auto Switching

Selected Clock

Free Run Mode Programming Procedure

Clock Control Logic in Free Run Mode

Free Run Reference Frequency Constraints

While in Free Run

Digital Hold

Parameters in History Value of M

Digital Hold History Delay

Digital Hold History Averaging Time

VCO Freeze Si5319, Si5325, Si5367, Si5375

Digital Hold versus VCO Freeze

Coarse Skew Control Si5326, Si5368

Output Phase Adjust Si5326, Si5368

Unlimited Coarse Skew Adjustment Si5326, Si5368

Fine Skew Control Si5326, Si5368

Independent Skew Si5324, Si5326, Si5368, Si5369, Si5374

Frame Synchronization Realignment Si5368 and Ckconfigreg =

Output Phase Adjust Si5324, Si5327, Si5369, Si5374

Input-to-Output Skew All Devices

CKIN3/CKIN4 Frequency Selection Ckconf =

CKINn Frequency kHz Divisor

CKOUT2 Frequency MHz NC5 Divider Setting KHz Fsout

Common NC5 Divider Settings

Alignment Alarm Trigger Threshold

Alarm Trigger Threshold Units of T CKOUT2

Including Fsync Inputs in Clock Selection Si5368

Using Fsout as a Fifth Output Clock Si5368

Fsync Skew Control Si5368

Fsout Polarity and Pulse Width Control Si5368

Output Signal Format Selection

Disabling CKOUTn

Clock Validation Time

Loss-of-Signal Validation Times

Loss-of-Signal Registers

LOS Selection

FOS Algorithm Si5324, Si5325, Si5326, Si5368, Si5369, Si5374

FOS Reference

FOS Reference Clock Selection

CLKnRATE Registers

Si5326 Si5368

LOS Si5319, Si5375

Fosen

Alarm Output Logic Equations Si5368 and Ckconfigreg =

11.6. C1B, C2B, C3B, Alrmout Si5368 Ckconfigreg =

Lock Detect Retrigger Time Lockt

Device Interrupts

I2C Command Format

13. I2C Serial Microprocessor Interface

SPI Command Format

Serial Microprocessor Interface SPI

InstructionBYTE0 Address/Data70BYTE1

Default Device Configuration

Register Descriptions

High-Speed I/O

Input Clock Buffers

CML/LVDS Termination 1.8, 2.5, 3.3

Output Driver Configuration

Typical Output Circuits

Disabling Unused Output Driver

Output Driver Si5365, Si5366 Si5325, Si5326, Si5367, Si5368

Output Format Measurements1,2

Typical Clock Output Scope Shots

Name Sfout Pin Sfout Code Single Diff Vocm Vpk-pk

Sfout2, Cmos

Sfout3, lowSwingLVDS

Sfout5, Lvpecl

Sfout7, Lvds

Cmos External Reference Circuit

OSC-P

Three-Level 3L Input Pins No External Resistors

Parameter Symbol Min Max

Three-Level 3L Input Pins With External Resistors

Power Supply

Typical Power Supply Bypass Network Tqfp Package

Packages and Ordering Guide

XA/XB Reference Sources and Frequencies

Resonator/External Clock Selection

Approved Crystals

RATE10

Fundamental Mode Crystals Reference Drift

Reference Jitter

38.88MHz XO, 38.88MHz CKIN, 38.88MHz Ckout

Phase Noise versus f3, 155.52 MHz in, 622.08 MHz out

Phase

High f3 Value

Offset Frequency Hz

DBc/Hz Noise

Yellow-696.399 MHz output Blue-622.08 MHz output

Reference vs. Output Frequency

MHz in, 622.08 MHz out, 696.399 MHz out

MHz Out Jitter Bandwidth Yellow, fs RMS Blue, fs RMS

High Reference Frequency

MHz thru 163 MHz Ext Ref, 155.52 MHz in, 622.08 MHz out

SONETOC192B, 4 MHz to 80 MHz

MHz thru 180 MHz Ext Ref, 155.52 MHz in, 622.08 MHz out

SONETOC192A, 20 kHz to 80 MHz

SONETOC192C, 50 kHz to 80 MHz

Appendix C-TYPICAL Phase Noise Plots

52 MHz In 622.08 MHz Out Loop BW = 7 Hz, Si5324

44 MHz In 156.25 MHz Out Loop BW = 80 Hz

44 MHz In 156.25 MHz Out Loop BW = 5 Hz, Si5324

130

44 MHz In 491.52 MHz Out Loop BW = 7 Hz, Si5324

08 MHz In 672.16 MHz Out Loop BW = 6.9 kHz

08 MHz In 672.16 MHz Out Loop BW = 100 Hz

25 MHz In 155.52 MHz Out

125 MHz In 644.531 MHz Out Jitter Values for Figure

Jitter Bandwidth 644.531 MHz Jitter RMS

125 MHz In 690.569 MHz Out Jitter Values for Figure

Jitter Bandwidth 690.569 MHz Jitter RMS

125 MHz In 693.493 MHz Out Jitter Values for Figure

Jitter Bandwidth 693.493 MHz Jitter RMS

Offset Frequency Hz

MHz in, 173.371 MHz and 693.493 MHz out

DBc/Hz

Jitter Values for Figure

685 MHz In 173.371 MHz Out

685 MHz In 693.493 MHz Out

MHz and 156.25MHz in, 622.08 MHz out

DBc/Hz

Jitter Bandwidth MHz Input Jitter RMS

MHz In 1 GHz Out

Digital Video HD-SDI

MHz in, 148.5 MHz out

Jitter Band

Appendix D-ALARM Structure

Si5368 Alarm Diagram 1

Si5368 Alarm Diagram 2

Pin # Si5316 Pull?

Si5316 Pullup/Down

Si5322 Pullup/Down

Pin # Si5322 Pull?

Pin # Si5323 Pull?

Si5323 Pullup/Down

Si5319, Si5324, Pullup/Down

Pin # Si5326 Pull?

Si5325 Pullup/Down

Si5326 Pullup/Down

Pin # Si5325 Pull?

Pin # Si5327 Pull?

Si5327 Pullup/Down

Si5365 Pullup/Down

Pin # Si5365 Pull?

Si5366 Pullup/Down

Pin # Si5366 Pull?

Pin # Si5367 Pull?

Si5367 Pullup/Down

Si5368 Pullup/Down

Pin # Si5368 Pull?

Si5369 Pullup/Down

Si5374/75 Pullup/Down

Pin # Si5374/75 Pull?

Bypass 622.08 MHz In, 622.08 MHz Out

MHz in, 622.08 MHz out

Power Supply Noise Rejection

Power Supply Noise to Output Transfer Function

MHz in, 155.52 MHz out Bandwidth = 110 Hz

Out No crosstalk 155.52 MHz

Clock Input Crosstalk Results Test Conditions

Jitter Band MHz MHz out 622.084 MHz

Hz loop KHz loop

Clock Input Crosstalk Phase Noise Plots

5 .5 2 1 M H z in , 6 2 2 .0 8 4 M H z o u t

Clock Input Crosstalk Detail View

155 .521 MHz in, 622 .084 MHz ou t

Clock Input Crosstalk Wideband Comparison

155 .521 M H z in, 622.084 M H z out

Clock Input Crosstalk Output of Rohde and Schwartz RF

Output Format vs. Jitter

Jitter vs. Output Format 19.44 MHz In, 622.08 MHz Out

Spectrum Analyzer Agilent Model E444OA

Hz in, 622.08 M Hz out

MHz External XA-XB Reference

Test Conditions

Input Frequency Variation = ±50 ppm

Jitter, fs

Input Frequency

Input Frequency Variation = ±2000 ppm

Jitter Values

Fmod Fdev Jitter Start RF Gen Si5326 Si5324

MHz in, 622.08 MHz out

RF Generator, Si5326, Si5324 No Jitter For Reference

RF Generator, Si5326, Si5324 100 Hz Jitter

RF Generator, Si5326, Si5324 1 kHz Jitter

RF Generator, Si5326, Si5324 10 kHz Jitter

Appendix I-Si5374AND Si5375 PCB Layout Recommendations

Ground Plane and Reset

Output Clock Routing

Oscp Oscn

Si5374, Si5375 Crosstalk Test Bed

Si5374/75 Crosstalk Jitter Values

Jitter, fsec RMS

Si5374, Si5375 Dspll a

Si5374, Si5375 Dspll B

Si5374, Si5375 Dspll C

Si5374, Si5375 Dspll D

Revision 0.41 to Revision

Revision 0.3 to Revision

Revision 0.4 to Revision

Revision 0.42 to Revision

Rev 179

Contact Information

![]()