XLi Ieee 1588 Clock

Page

Table of Contents

User Interfaces

SSS Ssssssssssssssssss Sssssssssssssssssss

XLi-Generated Messages

Snmp

Viii

Standard Configuration

Overview

Description

Physical

Related Specifications

Ieee 1588 card

Ieee 1588 Subsystem

User Interface

Network Port

PPS Output Sync OUT

Behavior

GPS C/A Receiver

LEDs

Introduction

Specifications

Standard Tcvcxo Oscillator

Related topics

Standard 110 VAC Power Supply

DAC

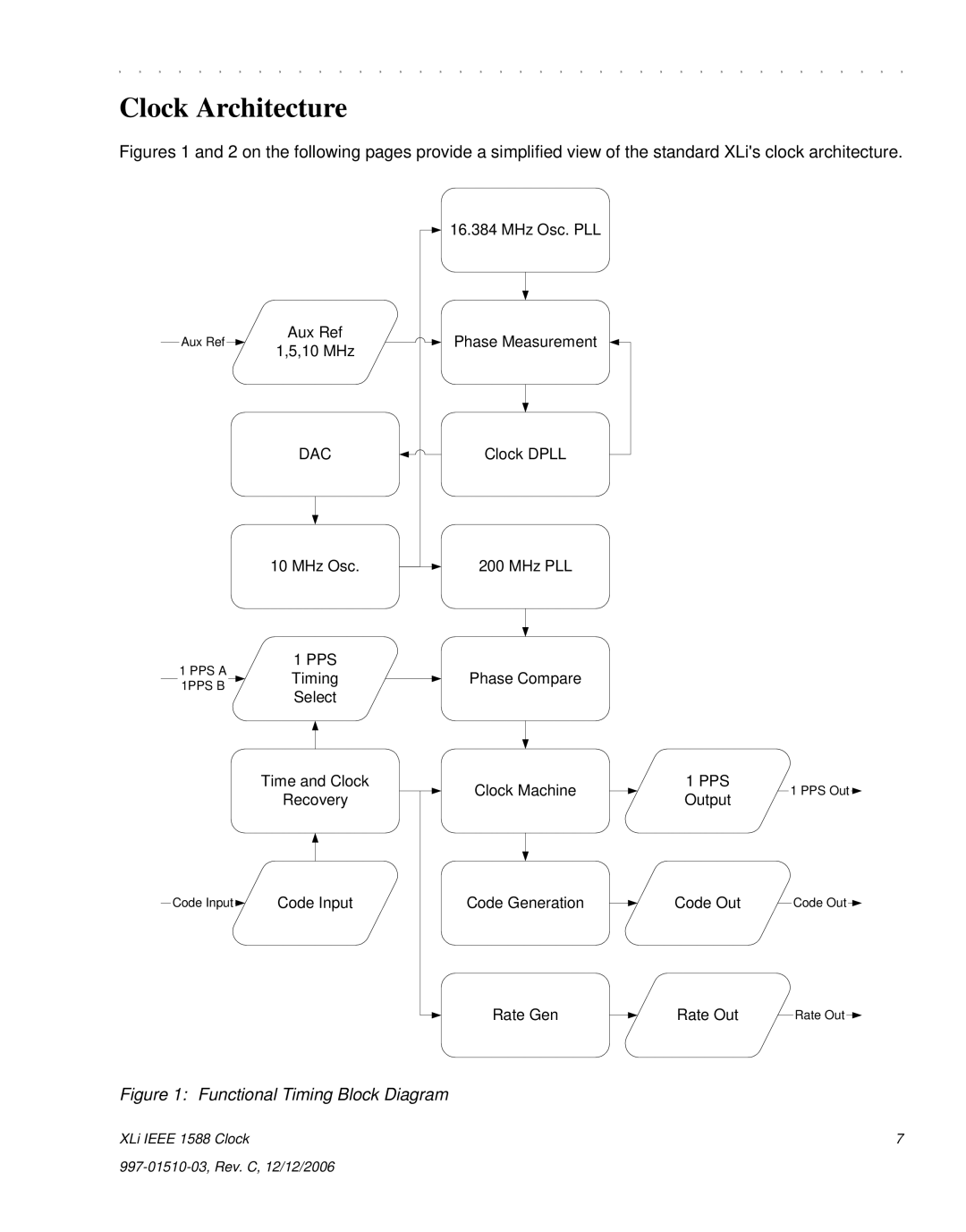

Clock Architecture

Interface Architecture Block Diagram

Mechanical/Environmental

AC Power Supply

Aux Ref Input

System Time & Frequency Accuracy

Chassis

GPS Receiver

Standard Inputs and Outputs

Serial I/O Port

NET Network Port

J2 Output Rate Out

J1 Input Time Interval Event Time

Auxiliary Reference Aux Ref

J3 Input Auxiliary Reference

PPS Pulse Per Second Output

Code Time Code Output

Certifications

Alarm Output

Selecting a GPS Antenna Site

Installing the GPS Antenna

Mounting the GPS Antenna

Verifying the Site

L1 GPS Antenna methods for cabling and mounting

GPS Signal Strength Requirements

GPS Signal Strength Requirements

Making Additional Connections and Powering Up

Configuring the XLi

Configuring Network Settings

PTP Master

Configuring the Ieee 1588 Cards

Slave Sync Threshold 5 microsec

PTP Slave

Rack Mounting the XLi

Secure the brackets to the rack using rack mount screws

997-01510-03, Rev. C, 12/12/2006

Alarm Status LED

Keypad/Display Interface

Time Display

Locked ∗ GPS PRI UTC

Status Display

Menu Display

Where

Time Zone Offset

Keypad Operation

Keypad Examples

To open a function using Menu

To change the settings in a function, and not save them

Other ways to abandon new settings in a function

Logging

Command Line Interface

Operator Login

Guest Login

Logging Out

Changing Username and Password

Session Timeout and Priority

You can log out using any of the following commands

Web Interface

User Privileges

Network port session

User Names and Passwords

Sessions

Navigating

Submitting Changes

997-01510-03, Rev. C, 12/12/2006

Function Summary

Function Reference

Snmp

F100 K I L L Reboot

Sign

F1 Time Zone Offset

For example, to set the time zone offset, enter

F1SSIGNHHMMCRLF

Separately from

F2 12/24 Hour Format

XLi responds

To verify the change, enter

F2SDHHSEPIHHCRLF

F3 Time & Date

For example, to display the current hour format, send

To set the hour format, send

SEP

Time Mode =

To display the time and date, send

F3CR

To set the time and date, send

F4 Serial Port Configuration

To display the Serial Port settings, send

For example, to display the date and time, send

F4 232 9600 8 none 1CRLF

F5 Time-Quality Setup

For example, to display the serial port settings, send

To set the serial port settings, send

XLi responds The XLi responds

F5CR

F5SSTATESEPFLAGSEPFLAGSEPFLAGSEPFLAGCRLF

F6CR

F5 Enable 2000 20000 200000 2000000CR

F6 Keypad Lock

To display the Keypad Lock status, send

For example, to display the Keypad Lock status, send

To enable Keypad Lock, send the following string

To disable Keypad Lock, send the following string

F8 Continuous Time Once-per-Second

Sohdddhhmmssqcrlf

F5 Time-Quality Setup F11 Time Output Format F69 Time Mode

Factory setting for the output string format is as follows

Format of the F8 Output String

F8CR

While Synchronizing to a Reference Source

After Loosing a Reference Source

XLi replies

F9 Time On Request

For example, to prepare Time on Request, enter

SOHDDDHHMMSS.mmmQCRLF

F11 responds

To display the default format for F11, enter

F11 Time Output Format

To exit F9 press Ctrl-C on your keyboard

F11 D

When you check the results by entering F11, F11 responds

To see the resulting change to F11, enter

F11, with DDD suppressed, responds

F9 displays

F13 Time Error

For example, to display the time error, enter

With the new formatting, F8 displays

F18CR

F18 Software Version Request

F50 B1 Llacr

F50 B1 Xyzcr

F51 GPS Antenna Cable Delay

XLi responds using the following format

For example

F51 B4CR

F51SBNSEPSIGNDELAYnsCRLF

Delay

F51SBNCR

F51 B4 100NSCR

F52 Distribution Cable Delay

To display the current distribution cable delay, enter

F52SEPSIGNDELAYnsCRLF

F52 +000060nsCR

F53 GPS Operation Mode

To set the distribution cable delay to 60 ns, enter

F52 +000000nsCRLF

For example, enter

F53 responds using the following format

If an GPS C/A Receiver is available, F53 displays

To save changes, press Enter

F53 responds

Or Dynamic Mode

F60 GPS Receiver Satellite List

Example response

Type

Level

F60 B1 Allcr

F60 B1 Currentcr F60 B1 Trackedcr

F66 OffCR

F66 Daylight Saving Time DST Mode

For example, to disable DST, enter

F66CR

F66 Manual 0 CR

Where

XLi responds to all changes with

F66 Manual 02 1 1 04 02 0 1

Important interactions between F69 and the IEEE1588 card

F69 Time Mode

F69 Local Crlf F69 Standard Crlf

Related functions

XLi gives one of the following responses

F69CR

F71 Oscillator Statistics

For example, to change the time mode to local time, enter

Or, to change the time mode to UTC, enter

To display the F71 settings, enter

DAY

F72 Fault Status

To display the status of the fault detectors, enter

EXP

F72CR

F73 Alarm Control / Status

DAC

Alarms General Information

GPS PRI OK Alarm Enabled

F73CR

F73SSSTATUSSOURCES123456789ABCDECRLF

Source

To clear the Alarm Latches, enter

F73SLATCHSEP123CRLF

F73SMASKSEPM12346789ABCDECRLF

For example, to enter new mask settings, enter

XLi replies To verify the changes, enter

F73SMASKSEP123456789ABCDECR

To disable LED Blink, enter

To view the Time Threshold setting, enter

To view Timeout Delay, enter

To enable LED Blink, enter

F74 Clock Source Control

F74CR

F90 Code Output Configuration

To display the current settings, enter

XLi responds, using the following format

Code Output

To change the Code Output selection enter

F90CR

F90SCODE Outputtypecr

Group

F100 Network Port Configuration & XLi Firmware

Description F100 followed by Comments

F100SIPCR

F100 EA Ethernet Address

F100 IP IP Address

F100 Eacr

F100 IP 192.169.46.150 SM255.255.255.0 G 192.168.46.1CR

F100 SM Subnet Mask

F100 IP 206.54.0.21CR

F100 Ipcr

F100 G Gateway

F100 GCR

F100 IC Network Port Settings

F100 Baset 10/100 BASE- T

F100 G 206.54.0.17CR

OK Crlf Reseting the Unitcrlf Please WAIT…CRLF

F100 L/LOCK/UNLOCK Remote Lockout

F100 Baset 10TCRLF

GOODBYE.CRLF

F100 L Remote Lockout

To users on the serial port, XLi responds

Or use the keypad/display’s F100

F100 ST Self Test Status

F100 L Lockedcrlf F100 L Unlockedcrlf

F100SSTCR

F100 BUB Burn BootLoader

F100 BH Burn Host

F100 BH 10.1.7.20 truetime/xli/192-8001.binCR

F100 Bucr

F100 BU Burn

And, for example, displays the following text

F100 Bubcr

F100 bf Burning File 192-8002.fs with Size 524288 SEC

F100 BF Burn File System

F100 Bufp Burn Fpga Firmware

F100SBFCR

Flash Successfully Programmed

F100 Config Configure NTP & Snmp

F100 config snmp set hostIP Address dirsubdirCR

F100 J Factory Mode Jumper

Here’s an example of a successful Snmp config file transfer

F100 config snmp get hostIP Address dirsubdirCR

F100 Ksislslcr

F100 K I L L Reboot

F100SJCR

F100 J Factory MODE=1CRLF F100 J Factory MODE=0CRLF

Initialization Successfully Completed

F100 P Change User Password

Flash File System Mounted

Scanforoptcard Begins

F100 Pisip AddressCR

When you enter the new password, the XLi responds

F100 PI Ping

Unit responds example

F100 Picr

When you enter a new user name, The XLi responds

F100 PN Change User Name

Or it responds

F108SCR

F108 Oscillator Configuration

F108SOSCILLATORSCONFIGSOSCCRLF

High High Stability Ocxo

OSC =

F108 Oscillator Config Tcvcxocrlf

F110 J1 Input Tiet

For example, enter the following string

F110CR

Function responds with the Ascii character string

Tiet

F110 Tiet 50 Positivecrlf

Then configure Tiet example

F111 J2 Output Rate

To obtain Tiet measurement from J1, enter

F111CR

To request the J2 Output Configuration, enter the following

XLi responds in the following format

Displays a fixed 10 PPS rate output example

F113 J3 Input Configuration Aux Ref

For example, to produce a fixed 100 kPPS rate output, enter

Auxiliary Reference Aux Ref Input

XLi displays the current configuration example

To display the J3 Input Configuration, enter

XLi responds using the following formats

Where the F113 entry and request formats are defined as

To all of the above examples, the XLi responds

Or, to disable F113, enter

F113 Disablecrlf

F116 Display Brightness Level

Freq Meas =

F117 Factory Configuration

F117CR

NTP

F118SBNCRLF

F118 Option Board Configuration

F118 B1 GPS M12 Receiver

F118SBNSOCCRLF

OC =

F118 B1CR

This information is useful for identifying the option card

F119 GPS Receiver Configuration

Unlocked GPS PRI Local

Locked GPS PRI Local

233182129

F119SBNSEPSCR

To obtain the status of the GPS Receiver, enter

F119 B1 CCR

F119SBNSCSCONFIGCR

F119 B1 S

F119SBNSCCR

F119 B1 C Pricrlf

For example to make it a primary reference source, enter

F126S5674397586090CR

F126 Options Key Entry

F128 Have Quick Output

F126SKCCRLF

PTP Technology Ethernet PTP NO. of Ports PTP Stratum

F130 Precision Time Protocol Status

PTP Part Number

F130SPBNSEPS

118 XLi Ieee 1588 Clock

Option bay location of the Ieee 1588 cards

F131 Precision Time Protocol Network Config

PTP Sync message interval

Dhcp enabled/disabled

PTP subdomain same

PTP burst mode enabled/disabled

PTP network port enabled/disabled

Reset PTP settings to factory defaults

PTP Preferred Master Configuration

PTP Master or Slave PRI/SEC/STBY

PTP Slave Synchronization Threshold

F131 BN F131 B4

Error Invalid Command

Request the PTP Protocol settings

Set the Default Gateway

Request the Dhcp settings

Enable/disable Dhcp

Set Internet Configuration settings

Request a summary of the PTP card configuration

Set the Subnet Mask

Set the IP Address

Set the Default Gateway

To get the Default Gateway, enter

To set the Default Gateway, enter

Response

Setting the Internet Configuration

Enable/Disable Dhcp

To get the Dhcp setting, enter

F131 B4 Protocol 27 Enable Enablecrlf

Get PTP Protocol settings

To get PTP protocol settings, use the following format

To set the PTP protocol settings, use the following format

To set the PTP Subdomain Name, use the following format

Request the PTP Subdomain Name

Set the PTP Subdomain Name

To request the PTP Subdomain Name, use the following format

Initialize the PTP Protocol to User-entered Values

Reset the PTP Parameters to the Factory Default settings

F131 B4 C

Configuring the PTP Reference Clock Settings

To change the settings, use the following format

F131 BN CCR

F131 B4 SST

Request the PTP Slave Synchronization Threshold

Set the PTP Slave Synchronization Threshold

F131 BN Sstcr

F131 B4 PM

Request the PTP Preferred Master Clock Configuration

F131 B4 PM Enablecrlf

Request PTP Network Parameter Status

Slave Sync Threshold 5 microsecCRLF

Preferred Master Enablecrlf

F131 B4 S

F131 B4CRLF

136 XLi Ieee 1588 Clock

XLi-Generated Messages

Error Messages

Error Action get or set is not specified

XLi has just terminated a session

Host configuration was successful

Informational Messages

Source file was successfully read

This page was intentionally left blank

Get the IP Address of the FTP Server/Workstation

Configuring Snmp Parameters

Set up the FTP Server

Overview of Steps

Copy the Configuration Files to the FTP Server

Edit the Configuration Files

F100 config snmp get hostIP Address dirsubdir

F100 config snmp set hostIP Address dirsubdir

Move the Configuration Files Back to the XLi

144 XLi Ieee 1588 Clock

Open a Command Line Session on the XLi

Overview of Procedure

Enter the following command

Upgrade the Firmware

Do the same for the ‘firmware’ .bin file

Then enter

Then do the same for the ‘file system’ .fs file

F100 bf

Troubleshooting

Then enter K space I space L space L as shown here

F100 bh 192.168.49.120 /192-8002.fs

Nvram VER Proj REV

Log on to the XLi and enter the following command

Bootloader

An example XLi response is

F100 IC F100 IP192.168.47.156 SM255.255.255.0 G192.168.47.1

SymmetricomTtm-SMIv2.mib

152 XLi Ieee 1588 Clock

Syntax Integer 0..2147483647 MAX-ACCESS read-only

154 XLi Ieee 1588 Clock

XLi Ieee 1588 Clock 155 997-01510-03, Rev. C, 12/12/2006

DTS

DCN

Nist

TSP

Syntax Integer 0..8 MAX-ACCESS read-only Status deprecated

Baud300 300, baud1200 1200, baud9600

GpsLongitude OBJECT-TYPE

Syntax Counter32 MAX-ACCESS read-only Status deprecated

160 XLi Ieee 1588 Clock

XliMainCard-SMIv2.mib

END

Organization Symmetricom INC CONTACT-INFO

= ntp NtpEstErr OBJECT-TYPE

Syntax Integer

NoLeapWarning

Field, ntpSysStratum, to 1. = ntp

Syntax Integer -127..127 MAX-ACCESS read-only Status current

Xli-SMIv2.mib

XliSystem-SMIv2.mib

MODULE-IDENTITY

SystemFaultConfigData

SystemAlarmData

SystemFaultConfig

SystemFaultHistory

LatchClear

168 XLi Ieee 1588 Clock

XLi Ieee 1588 Clock 169 997-01510-03, Rev. C, 12/12/2006

170 XLi Ieee 1588 Clock

XLi Ieee 1588 Clock 171 997-01510-03, Rev. C, 12/12/2006

172 XLi Ieee 1588 Clock

= systemStatusGeneral

Unlocked1 Locked MAX-ACCESS read-only

Locked1 Unlocked2

ClockIrigA

Gives the current status of the IRIG. = systemStatusDetail

Fault

StatusSecondaryPower OBJECT-TYPE Syntax Integer

Editing snmp.conf

Ok 1, fault 2 MAX-ACCESS read-only Status current

Key

Snmp Private Enterprise MIB Structure

Snmp Addressing

New Top Level Structure of Enterprise MIB for XLi

Additional Products

XLi System Group

XLi Fault Group

XLi System Status Group

XLi Traps

Future Expansion

XLi MainCard Group

Glossary of SNMP-Related Terms

Materials Needed

Configuring and Testing Snmp

HP OpenView Configuration

XLi unit PC with HP OpenView installed

Load the TrueTime Enterprise MIBs

Configure Traps

Test Procedure

XLi Configuration

Trap Testing

188 XLi Ieee 1588 Clock

Irig Code Format

Introduction

IRIG-B Time Quality Flags

Output

Input

Nasa 36 Code Format

Irig Standard Format a

World Map of Time Zones

194 XLi Ieee 1588 Clock

Time Interval Event Time Tiet on Main CPU J1 87-8026

Part Numbers

196 XLi Ieee 1588 Clock

Customer Assistance Center Telephone Numbers

Sales and Customer Assistance

198 XLi Ieee 1588 Clock

Glossary of Ieee 1588-related Terms

200 XLi Ieee 1588 Clock

Alarm Status

Cable Delay

Antenna

Error

Code Output Configuration

Configuration

Have Quick Configuration

F100 Config Configure NTP & Snmp Parameters

Guest Login User Name Password

Network

Network Settings

Keypad

Messages

Serial Port

Signal Strength Requirements

Oscillator

Rate Output

Snmp.conf Editing

Standard 12 VDC Power Supply

Fault

Snmp Private Enterprise MIB Structure

Username

Version

XLi

![]()

![]()

![]()

![]() 16.384 MHz Osc. PLL

16.384 MHz Osc. PLL