Assembly Source for Algorithms

PRELIMINARY

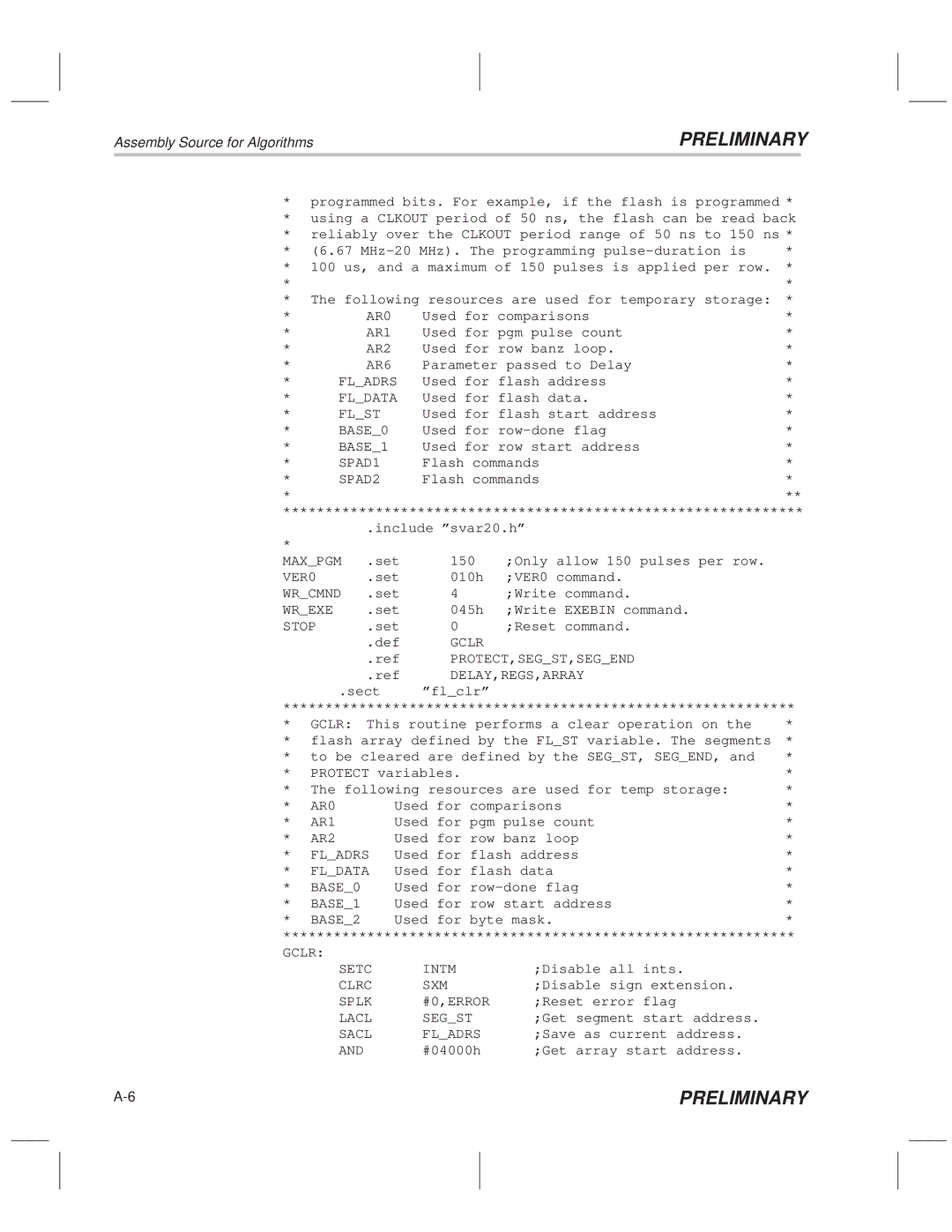

* programmed bits. For example, if the flash is programmed *

*using a CLKOUT period of 50 ns, the flash can be read back

* | reliably over the CLKOUT period range of 50 ns to 150 ns * | ||

* (6.67 MHz±20 MHz). The programming | * | ||

* 100 us, and a maximum of 150 pulses is applied per row. | * | ||

* |

|

| * |

* The following resources are used for temporary storage: | * | ||

* | AR0 | Used for comparisons | * |

* | AR1 | Used for pgm pulse count | * |

* | AR2 | Used for row banz loop. | * |

* | AR6 | Parameter passed to Delay | * |

* | FL_ADRS | Used for flash address | * |

* | FL_DATA | Used for flash data. | * |

* | FL_ST | Used for flash start address | * |

* | BASE_0 | Used for row±done flag | * |

* | BASE_1 | Used for row start address | * |

* | SPAD1 | Flash commands | * |

* | SPAD2 | Flash commands | * |

* |

|

| ** |

**************************************************************

| .include ºsvar20.hº | ||

* |

|

|

|

MAX_PGM | .set | 150 | ;Only allow 150 pulses per row. |

VER0 | .set | 010h | ;VER0 command. |

WR_CMND | .set | 4 | ;Write command. |

WR_EXE | .set | 045h | ;Write EXEBIN command. |

STOP | .set | 0 | ;Reset command. |

| .def | GCLR |

|

| .ref | PROTECT,SEG_ST,SEG_END | |

| .ref | DELAY,REGS,ARRAY | |

.sect | ºfl_clrº |

| |

*************************************************************

* | GCLR: This routine performs a clear operation on the | * | |

* flash array defined by the FL_ST variable. The segments | * | ||

* to be cleared are defined by the SEG_ST, SEG_END, and | * | ||

* | PROTECT variables. | * | |

* The following resources are used for temp storage: | * | ||

* | AR0 | Used for comparisons | * |

* | AR1 | Used for pgm pulse count | * |

* | AR2 | Used for row banz loop | * |

* | FL_ADRS | Used for flash address | * |

* | FL_DATA | Used for flash data | * |

* | BASE_0 | Used for row±done flag | * |

* | BASE_1 | Used for row start address | * |

* | BASE_2 | Used for byte mask. | * |

*************************************************************

GCLR: |

|

|

SETC | INTM | ;Disable all ints. |

CLRC | SXM | ;Disable sign extension. |

SPLK | #0,ERROR | ;Reset error flag |

LACL | SEG_ST | ;Get segment start address. |

SACL | FL_ADRS | ;Save as current address. |

AND | #04000h | ;Get array start address. |

PRELIMINARY |