PRELIMINARY

Erase Algorithm

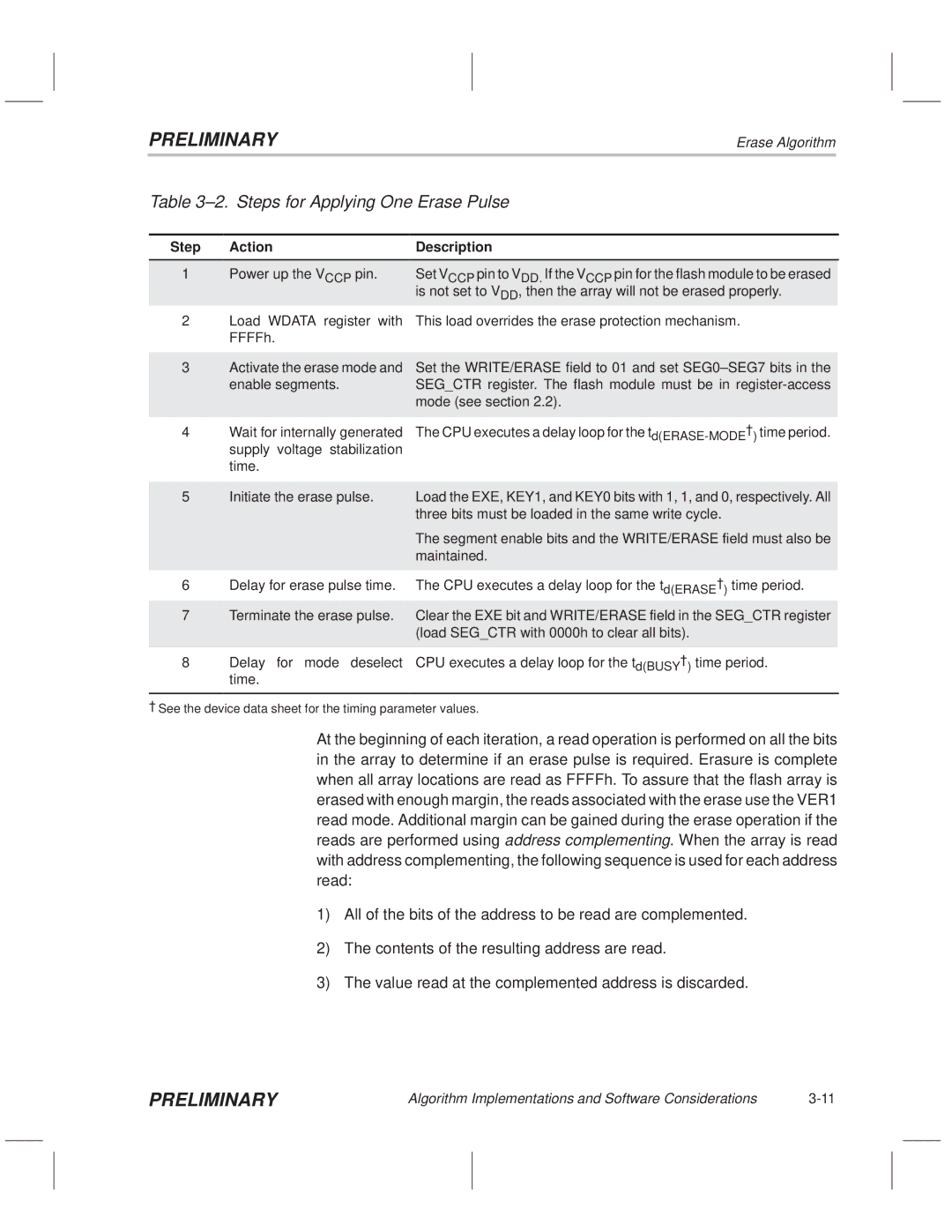

Table 3±2. Steps for Applying One Erase Pulse

Step | Action | Description |

|

|

1 | Power up the VCCP pin. | Set VCCP pin to VDD. If the VCCP pin for the flash module to be erased | ||

|

| is not set to VDD, then the array will not be erased properly. | ||

2 | Load WDATA register with | This load overrides the erase protection mechanism. |

|

|

| FFFFh. |

|

|

|

|

|

| ||

3 | Activate the erase mode and | Set the WRITE/ERASE field to 01 and set SEG0±SEG7 bits in the | ||

| enable segments. | SEG_CTR register. The flash module must be in | ||

|

| mode (see section 2.2). |

|

|

|

|

|

|

|

4 | Wait for internally generated | The CPU executes a delay loop for the t | ² | time period. |

| supply voltage stabilization |

| ||

|

|

|

| |

| time. |

|

|

|

|

|

| ||

5 | Initiate the erase pulse. | Load the EXE, KEY1, and KEY0 bits with 1, 1, and 0, respectively. All | ||

|

| three bits must be loaded in the same write cycle. |

|

|

|

| The segment enable bits and the WRITE/ERASE field must also be | ||

|

| maintained. |

|

|

|

|

| ||

6 | Delay for erase pulse time. | The CPU executes a delay loop for the td(ERASE² ) time period. | ||

7 | Terminate the erase pulse. | Clear the EXE bit and WRITE/ERASE field in the SEG_CTR register | ||

|

| (load SEG_CTR with 0000h to clear all bits). |

|

|

|

|

| ||

8 | Delay for mode deselect | CPU executes a delay loop for the td(BUSY² ) time period. | ||

| time. |

|

|

|

² See the device data sheet for the timing parameter values.

At the beginning of each iteration, a read operation is performed on all the bits in the array to determine if an erase pulse is required. Erasure is complete when all array locations are read as FFFFh. To assure that the flash array is erased with enough margin, the reads associated with the erase use the VER1 read mode. Additional margin can be gained during the erase operation if the reads are performed using address complementing. When the array is read with address complementing, the following sequence is used for each address read:

1)All of the bits of the address to be read are complemented.

2)The contents of the resulting address are read.

3)The value read at the complemented address is discarded.

PRELIMINARY | Algorithm Implementations and Software Considerations |