PRELIMINARY

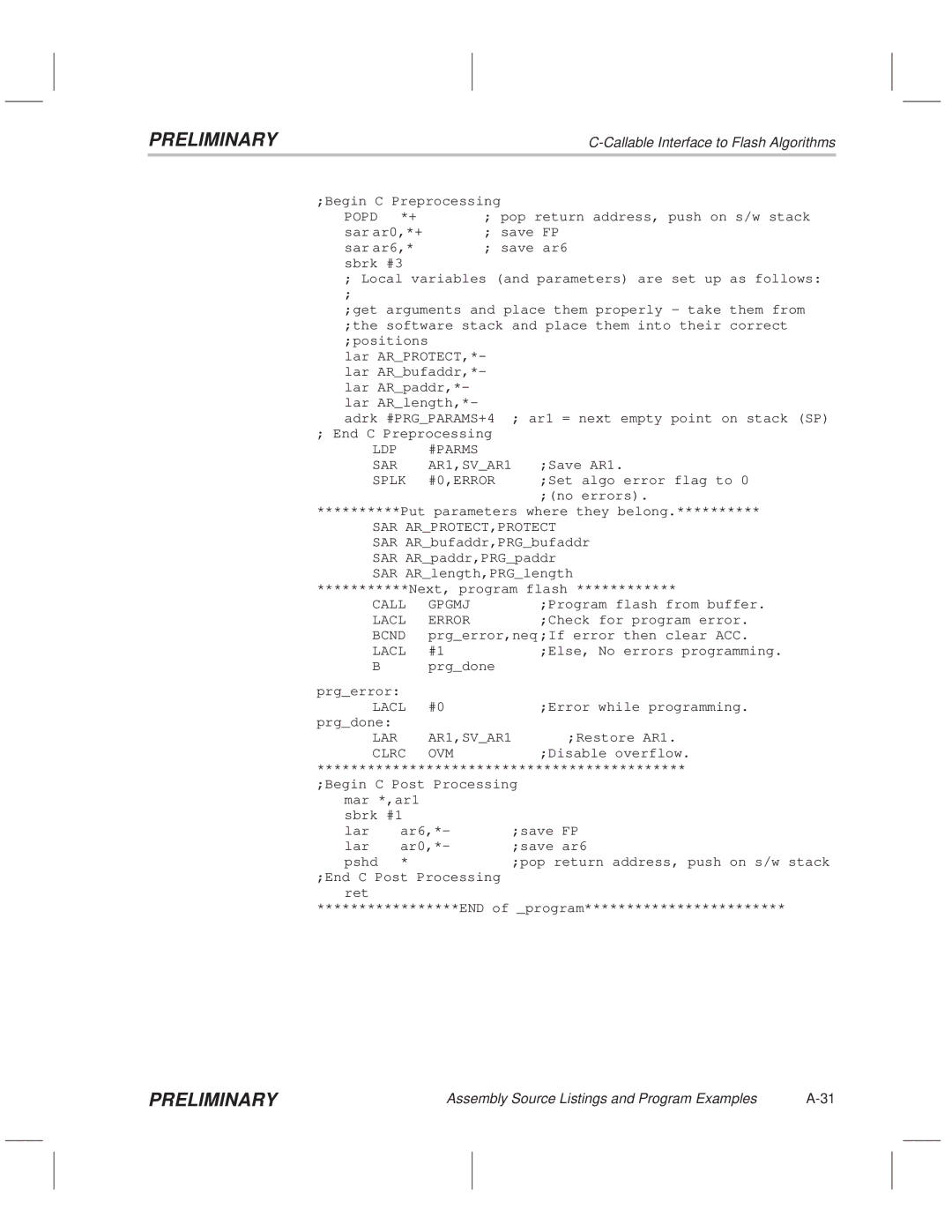

;Begin C Preprocessing

POPD *+ | ; pop return address, push on s/w stack |

sar ar0,*+ | ; save FP |

sar ar6,* | ; save ar6 |

sbrk #3 |

|

;Local variables (and parameters) are set up as follows:

;get arguments and place them properly ± take them from ;the software stack and place them into their correct ;positions

lar AR_PROTECT,*± lar AR_bufaddr,*± lar AR_paddr,*± lar AR_length,*±

adrk #PRG_PARAMS+4 ; ar1 = next empty point on stack (SP)

;End C Preprocessing

LDP | #PARMS |

|

SAR | AR1,SV_AR1 | ;Save AR1. |

SPLK | #0,ERROR | ;Set algo error flag to 0 |

|

| ;(no errors). |

**********Put parameters where they belong.**********

SAR AR_PROTECT,PROTECT SAR AR_bufaddr,PRG_bufaddr SAR AR_paddr,PRG_paddr SAR AR_length,PRG_length

***********Next, program flash ************

CALL | GPGMJ |

| ;Program flash from buffer. | |

LACL | ERROR |

| ;Check for program error. | |

BCND | prg_error,neq ;If error then clear ACC. | |||

LACL | #1 |

| ;Else, No errors programming. | |

B |

| prg_done |

|

|

prg_error: |

|

|

| |

LACL | #0 |

| ;Error while programming. | |

prg_done: |

|

|

|

|

LAR |

| AR1,SV_AR1 | ;Restore AR1. | |

CLRC | OVM |

| ;Disable overflow. | |

******************************************** | ||||

;Begin C Post Processing |

| |||

mar *,ar1 |

|

|

| |

sbrk #1 |

|

|

| |

lar | ar6,*± | ;save FP | ||

lar | ar0,*± | ;save ar6 | ||

pshd | * |

| ;pop return address, push on s/w stack | |

;End C Post Processing ret

*****************END of _program************************

PRELIMINARY | Assembly Source Listings and Program Examples |