Flash Module Control Registers

PRELIMINARY

2.3 Flash Module Control Registers

Table 2±2 lists the control registers and their relative addresses within the four locations that repeat throughout the module's address range.

Table 2±2. Flash Module Control Registers

Relative | Register | Description |

Address | Name | |

|

|

|

0 | SEG_CTR | Segment control register. The eight MSBs enable spe- |

|

| cific segments for programming. Setting a bit to 1 en- |

|

| ables the segment. The eight LSBs control the pro- |

|

| gram, erase, and verify operations of the module. |

Described in ...

Section Page

2.3.1

1 | TST | Test register. Reserved for test; not accessible to the | 2.3.2 | |

|

| user. |

|

|

|

|

|

|

|

2 | WADRS | Write address register. Holds the address for a write | 2.3.3 | |

|

| operation. |

|

|

|

|

|

|

|

3 | WDATA | Write data register. Holds the data for a write operation. | 2.3.4 | |

|

|

|

|

|

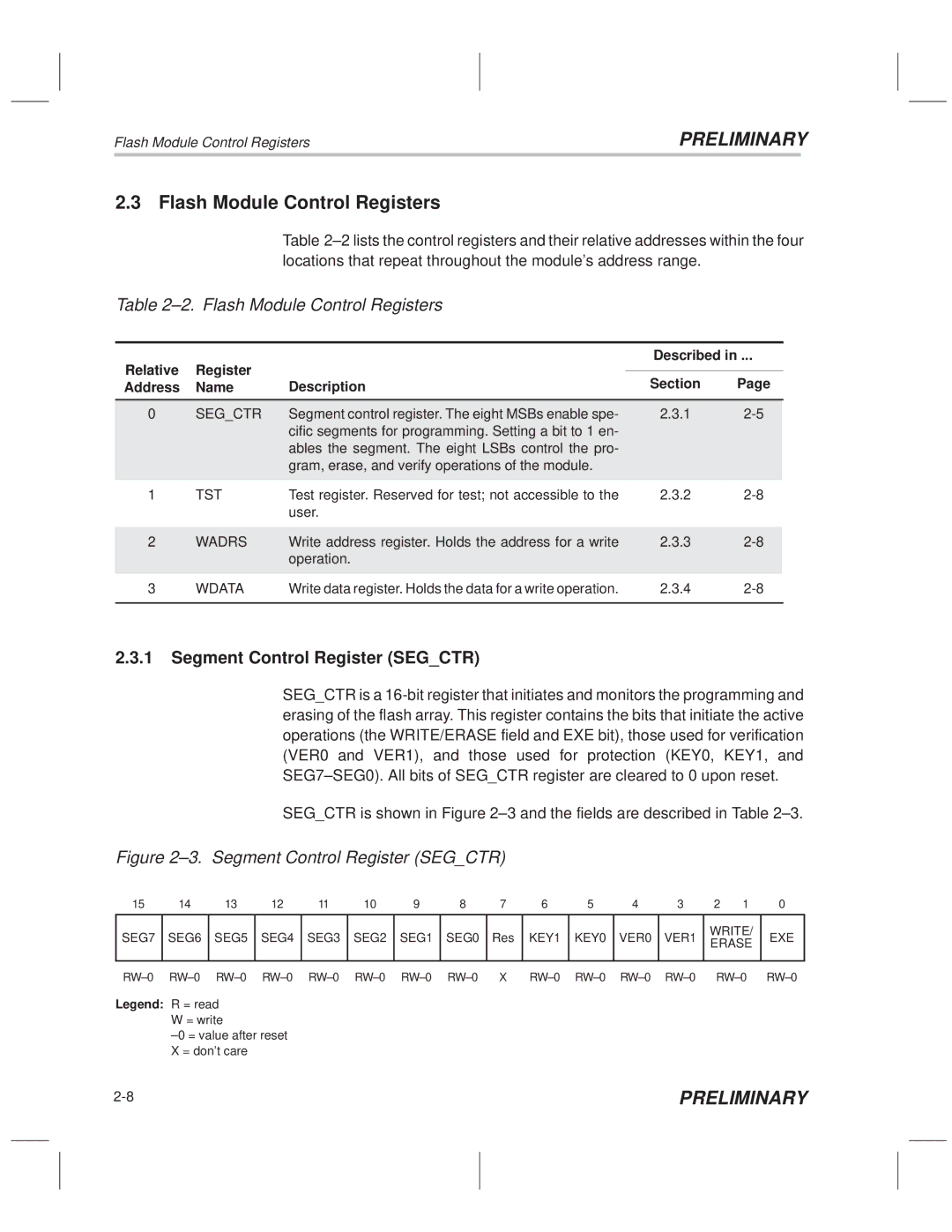

2.3.1Segment Control Register (SEG_CTR)

SEG_CTR is a

SEG_CTR is shown in Figure 2±3 and the fields are described in Table 2±3.

Figure 2±3. Segment Control Register (SEG_CTR)

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

SEG7 SEG6 SEG5 SEG4 SEG3 SEG2 SEG1 SEG0 Res

KEY1 KEY0 VER0 VER1

WRITE/ ERASE

EXE

RW±0 RW±0 RW±0 RW±0 RW±0 RW±0 RW±0 RW±0 X RW±0 RW±0 RW±0 RW±0 RW±0 RW±0

Legend: R = read

W = write

±0 = value after reset X = don't care

PRELIMINARY |