Using the Algorithms With C Code to Erase and Reprogram the 'F240

PRELIMINARY

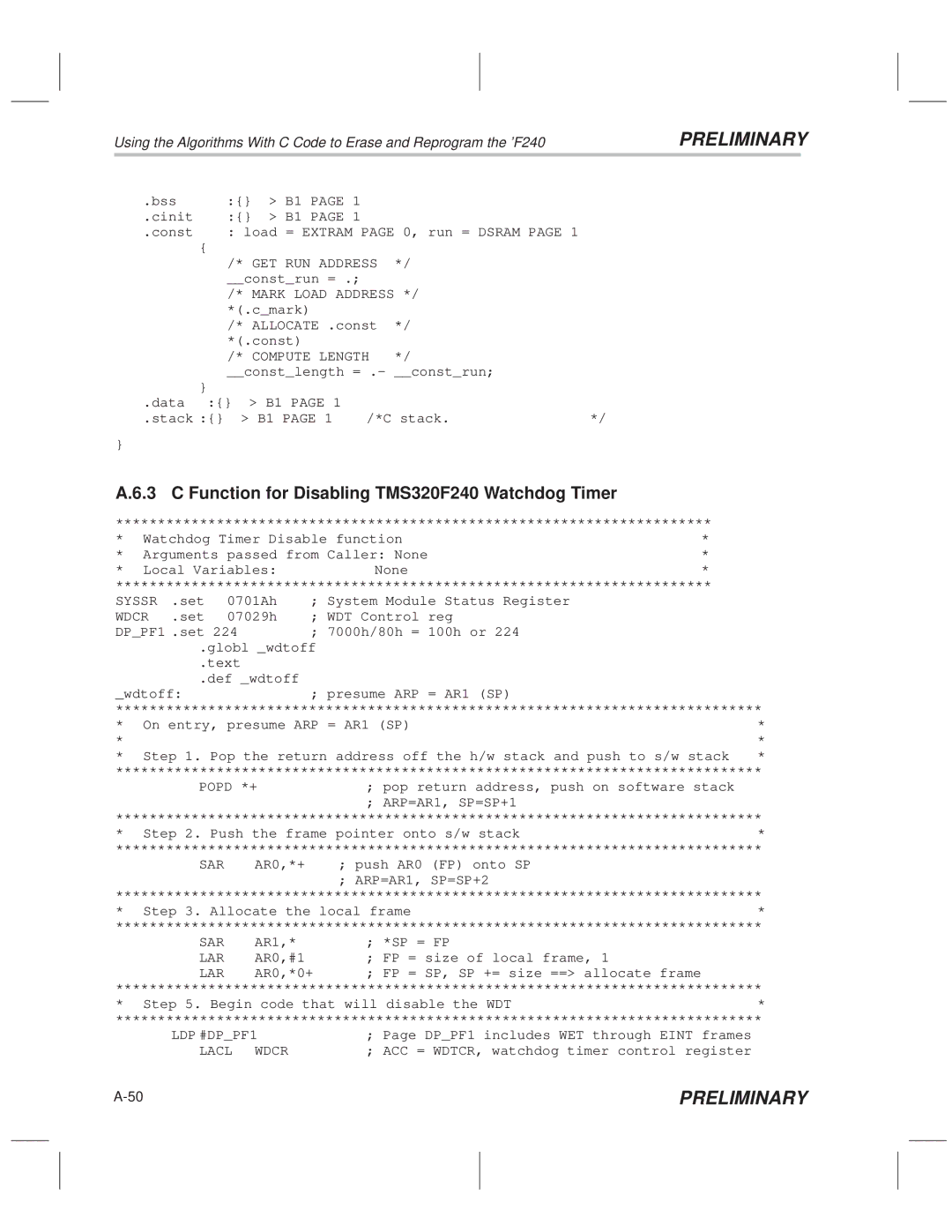

.bss | :{} | > | B1 | PAGE | 1 |

.cinit | :{} | > | B1 | PAGE | 1 |

.const | : load = EXTRAM PAGE 0, run = DSRAM PAGE 1 | ||||

| { |

|

|

|

|

/* GET RUN ADDRESS */ __const_run = .;

/* MARK LOAD ADDRESS */ *(.c_mark)

/* ALLOCATE .const */ *(.const)

/* COMPUTE LENGTH */

__const_length = .± __const_run;

} |

|

|

|

.data :{} | > B1 PAGE 1 |

|

|

.stack :{} | > B1 PAGE 1 | /*C stack. | */ |

}

A.6.3 C Function for Disabling TMS320F240 Watchdog Timer

***********************************************************************

* | Watchdog Timer Disable function | * | |

* Arguments passed from Caller: None | * | ||

* | Local Variables: | None | * |

***********************************************************************

SYSSR | .set | 0701Ah | ; System Module Status Register |

WDCR | .set | 07029h | ; WDT Control reg |

DP_PF1 .set 224 | ; 7000h/80h = 100h or 224 | ||

| .globl _wdtoff | ||

| .text |

| |

| .def _wdtoff |

| |

_wdtoff: |

| ; presume ARP = AR1 (SP) | |

*****************************************************************************

* On entry, presume ARP = AR1 (SP) | * | |

* |

| * |

* | Step 1. Pop the return address off the h/w stack and push to s/w stack | * |

*****************************************************************************

POPD *+ | ; pop return address, push on software stack |

;ARP=AR1, SP=SP+1

*****************************************************************************

* Step 2. Push the frame pointer onto s/w stack*

*****************************************************************************

SAR | AR0,*+ | ; push AR0 (FP) onto SP |

;ARP=AR1, SP=SP+2

*****************************************************************************

* Step 3. Allocate the local frame*

*****************************************************************************

SAR | AR1,* | ; *SP = FP |

LAR | AR0,#1 | ; FP = size of local frame, 1 |

LAR | AR0,*0+ | ; FP = SP, SP += size ==> allocate frame |

*****************************************************************************

* Step 5. Begin code that will disable the WDT*

*****************************************************************************

LDP #DP_PF1 | ; | Page DP_PF1 includes WET through EINT frames |

LACL WDCR | ; | ACC = WDTCR, watchdog timer control register |

PRELIMINARY |