Assembly Source for Algorithms

PRELIMINARY

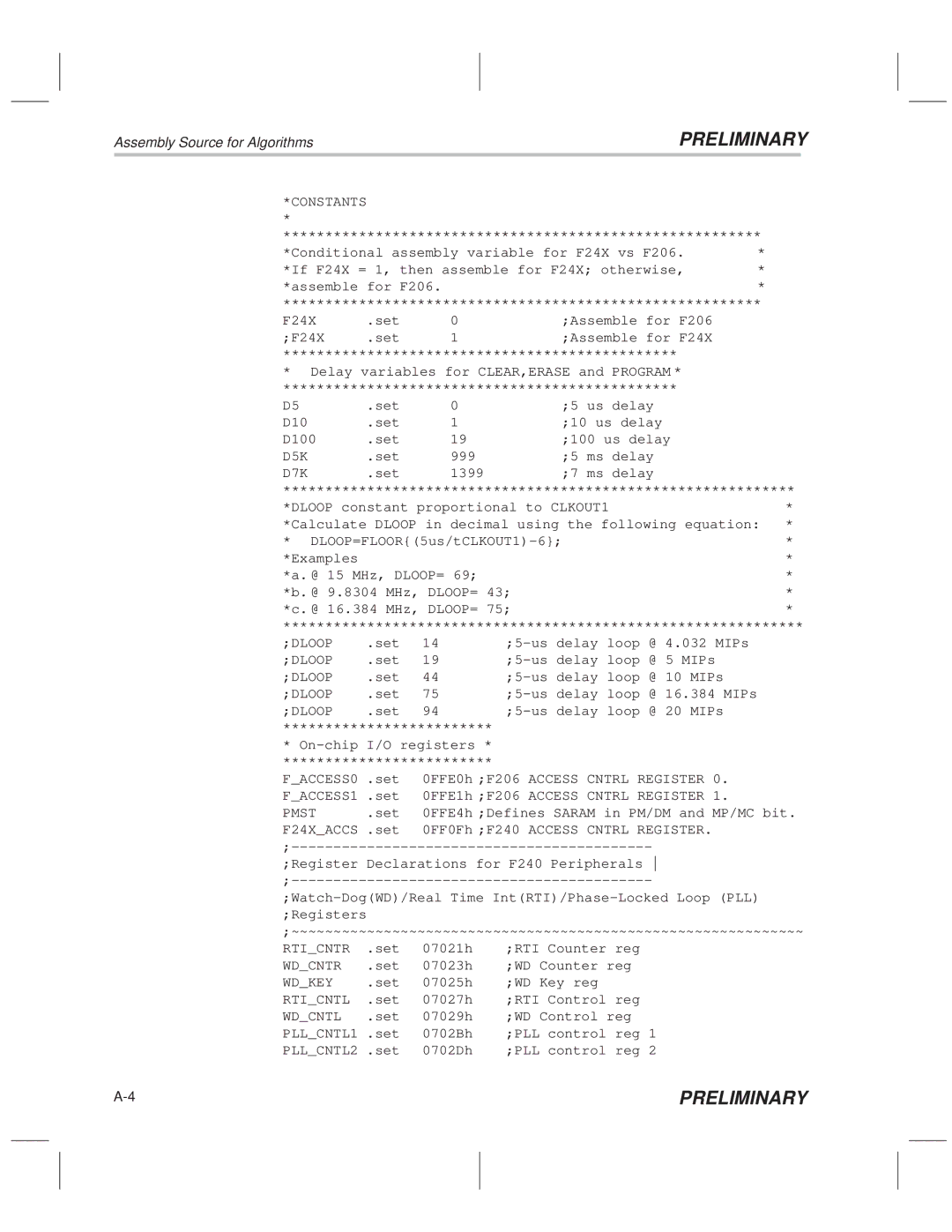

*CONSTANTS

*

*********************************************************

*Conditional assembly variable for F24X vs F206. | * |

*If F24X = 1, then assemble for F24X; otherwise, | * |

*assemble for F206. | * |

*********************************************************

F24X | .set | 0 | ;Assemble for F206 |

;F24X | .set | 1 | ;Assemble for F24X |

*********************************************** | |||

* Delay variables for CLEAR,ERASE and PROGRAM *

***********************************************

D5 | .set | 0 | ;5 us delay |

D10 | .set | 1 | ;10 us delay |

D100 | .set | 19 | ;100 us delay |

D5K | .set | 999 | ;5 ms delay |

D7K | .set | 1399 | ;7 ms delay |

*************************************************************

*DLOOP constant proportional to CLKOUT1* *Calculate DLOOP in decimal using the following equation: *

* DLOOP=FLOOR{(5us/tCLKOUT1)±6}; | * | ||

*Examples |

| * | |

*a. @ 15 MHz, DLOOP= 69; | * | ||

*b. @ | 9.8304 | MHz, DLOOP= 43; | * |

*c. @ | 16.384 | MHz, DLOOP= 75; | * |

**************************************************************

;DLOOP | .set | 14 | ;5±us delay loop @ 4.032 MIPs |

;DLOOP | .set | 19 | ;5±us delay loop @ 5 MIPs |

;DLOOP | .set | 44 | ;5±us delay loop @ 10 MIPs |

;DLOOP | .set | 75 | ;5±us delay loop @ 16.384 MIPs |

;DLOOP | .set | 94 | ;5±us delay loop @ 20 MIPs |

************************* |

| ||

* On±chip I/O registers * |

| ||

************************* |

| ||

F_ACCESS0 .set | 0FFE0h ;F206 ACCESS CNTRL REGISTER 0. | ||

F_ACCESS1 .set | 0FFE1h ;F206 ACCESS CNTRL REGISTER 1. | ||

PMST | .set | 0FFE4h ;Defines SARAM in PM/DM and MP/MC bit. | |

F24X_ACCS .set | 0FF0Fh ;F240 ACCESS CNTRL REGISTER. | ||

;±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±± ;Register Declarations for F240 Peripherals ;±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±± ;Watch±Dog(WD)/Real Time Int(RTI)/Phase±Locked Loop (PLL) ;Registers ;~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

RTI_CNTR | .set | 07021h | ;RTI Counter reg |

WD_CNTR | .set | 07023h | ;WD Counter reg |

WD_KEY | .set | 07025h | ;WD Key reg |

RTI_CNTL | .set | 07027h | ;RTI Control reg |

WD_CNTL | .set | 07029h | ;WD Control reg |

PLL_CNTL1 .set | 0702Bh | ;PLL control reg 1 | |

PLL_CNTL2 .set | 0702Dh | ;PLL control reg 2 | |

PRELIMINARY |