REGS

FL_ST

BASE_0 AR6,#D10 DELAY,*,AR6

ARRAY

;ACCESS FLASH REGS

;ACC => SEG_CTR.

;Activate MODE.

;SET DELAY ;WAIT

;ACCESS FLASH ARRAY

Assembly Source for Algorithms

PRELIMINARY

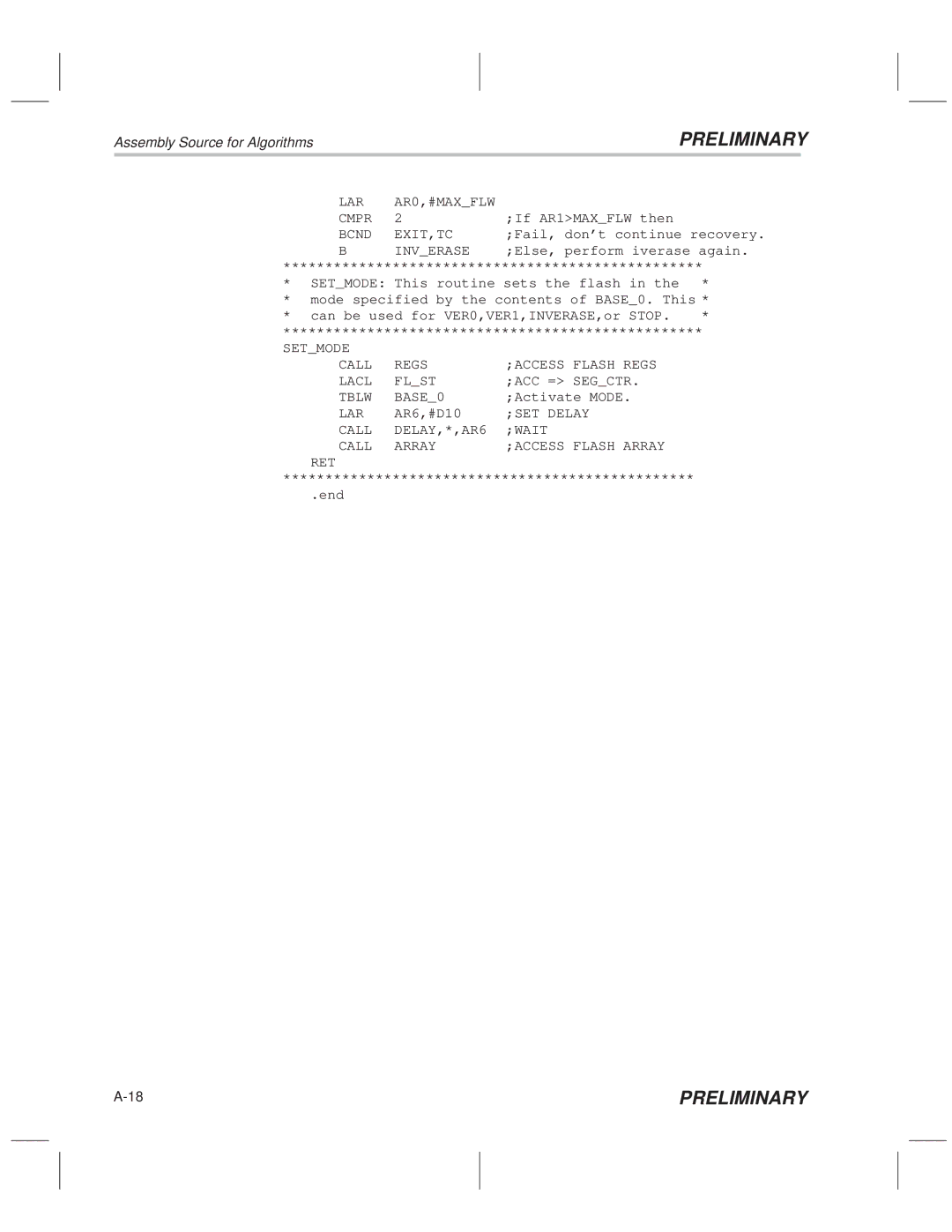

LAR | AR0,#MAX_FLW |

|

CMPR | 2 | ;If AR1>MAX_FLW then |

BCND | EXIT,TC | ;Fail, don't continue recovery. |

B | INV_ERASE | ;Else, perform iverase again. |

**************************************************

* SET_MODE: This routine sets the flash in the * * mode specified by the contents of BASE_0. This * * can be used for VER0,VER1,INVERASE,or STOP. *

**************************************************

SET_MODE CALL LACL TBLW LAR CALL CALL

RET

*************************************************

.end

PRELIMINARY |