CYV15G0404DXB

Independent Clock Quad HOTLink II™ Transceiver with Reclocker

Features

■Quad channel transceiver for 195 to 1500 MBaud serial signaling rate

❐Aggregate throughput of up to 12 Gbits/second

■

■Compliant to multiple standards

❐

❐10 bit uncoded data or 8B/10B coded data

■Truly independent channels

❐Each channel is able to:

•Perform reclocker function

•Operate at a different signaling rate

■Synchronous LVTTL parallel interface

■JTAG boundary scan

■Built In Self Test (BIST) for

■Link quality indicator by channel

❐Analog signal detect

❐Digital signal detect

■Low power 3W at 3.3V typical

■Single 3.3V supply

■256 ball thermally enhanced BGA

■0.25μ BiCMOS technology

■JTAG device ID ‘0C811069’x

• Transport a different data format

■Internal

■Selectable differential PECL compatible serial inputs per channel

❐Internal DC restoration

■Redundant differential PECL compatible serial outputs per channel

❐No external bias resistors required

❐Signaling rate controlled edge rates

❐Source matched for 50Ω transmission lines

■MultiFrame™ Receive Framer provides alignment options

❐Comma or full K28.5 detect

❐Single or multibyte Framer for byte alignment

❐Low latency option

■Selectable input and output clocking options

Functional Description

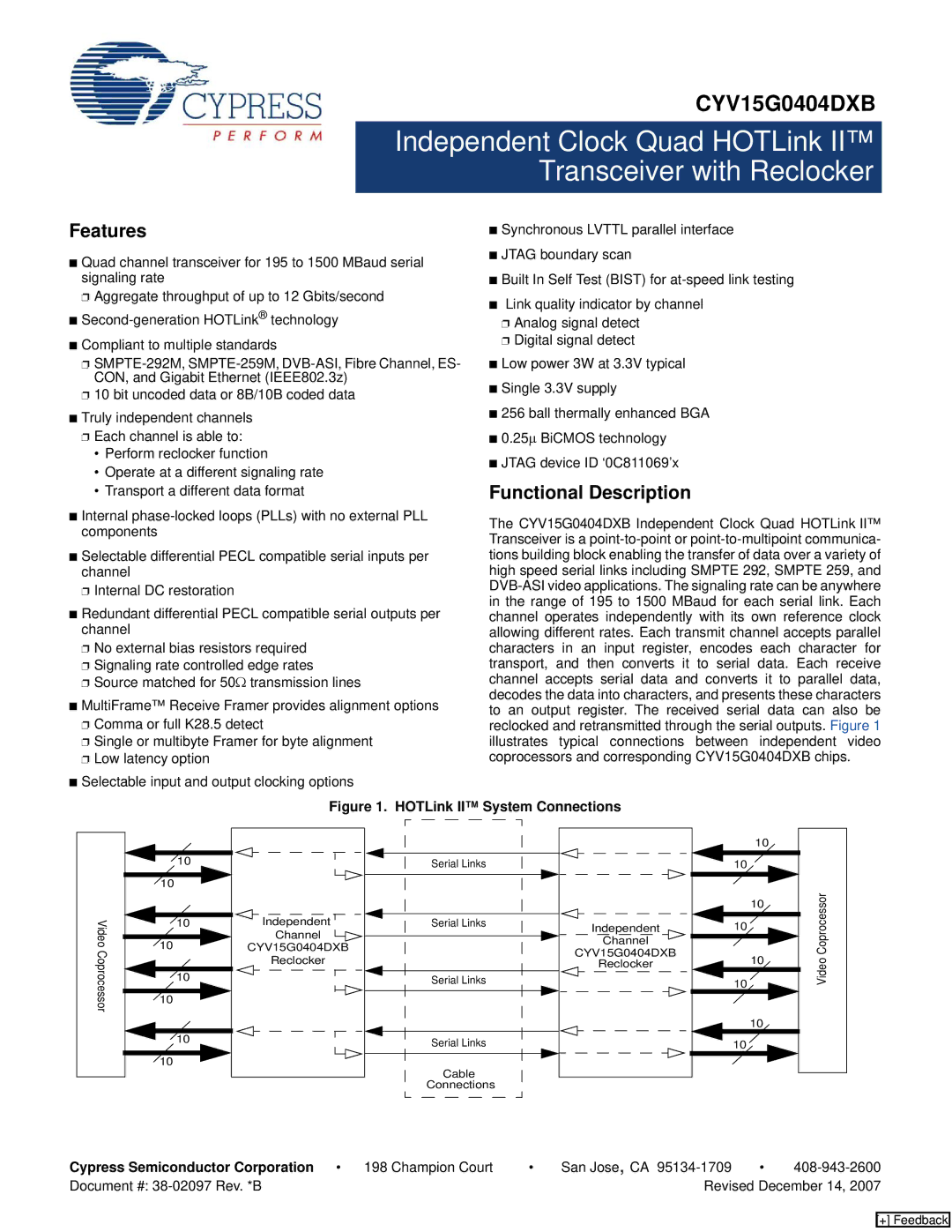

The CYV15G0404DXB Independent Clock Quad HOTLink II™ Transceiver is a

Figure 1. HOTLink II™ System Connections

| 10 |

| |

| 10 |

| |

Video | 10 | Independent | |

10 | Channel | ||

| |||

Coprocessor | CYV15G0404DXB | ||

| Reclocker | ||

|

| ||

| 10 |

| |

| 10 |

| |

| 10 |

| |

| 10 |

|

Serial Links

Serial Links

Serial Links

Serial Links

Cable

Connections

|

| 10 |

|

| 10 |

|

|

|

| 10 | Coprocessor |

Independent | 10 |

| |

Channel |

|

| |

CYV15G0404DXB |

| 10 | |

| Video | ||

Reclocker |

| ||

| 10 |

| |

|

|

| |

|

| 10 |

|

| 10 |

|

|

Cypress Semiconductor Corporation • 198 Champion Court | • | San Jose, CA | • | |

Document #: |

| Revised December 14, 2007 | ||

[+] Feedback