CYV15G0404DXB

The REFCLKx± inputs are differential inputs with each input internally biased to 1.4V. If the REFCLKx+ input is connected to a TTL, LVTTL, or LVCMOS clock source, the input signal is recognized when it passes through the internally biased reference point. When driven by a

When both the REFCLKx+ and REFCLKx– inputs are connected, the clock source must be a differential clock. This can either be a differential LVPECL clock that is DC- or

By connecting the REFCLKx– input to an external voltage source, it is possible to adjust the reference point of the REFCLKx+ input for alternate logic levels. When doing so, ensure that the input differential crossing point remains within the parametric range supported by the input.

Serial Output Drivers

The serial output interface drivers use differential Current Mode Logic (CML) drivers to provide source matched drivers for trans- mission lines. These drivers accept data from the transmit shifters. They have signal swings equivalent to that of standard PECL drivers, and are capable of driving

Transmit Channels Enabled

Each driver can be enabled or disabled separately using the device configuration interface.

When a driver is disabled through the configuration interface, it is internally powered down to reduce device power. If both serial drivers for a channel are in this disabled state, the associated internal logic for that channel is also powered down. A device reset (RESET sampled LOW) disables all output drivers.[8]

CYV15G0404DXB Receive Data Path

Serial Line Receivers

Two differential line receivers, INx1± and INx2±, are available on each channel for accepting serial data streams. The active serial line receiver on a channel is selected using the associated INSELx input. The serial line receiver inputs are differential, and can accommodate wire interconnect and filtering losses or trans- mission line attenuation greater than 16 dB. For normal operation, these inputs should receive a signal of at least VIDIFF> 100 mV, or 200 mV

Notes

The local internal loopback (LPENx) allows the serial transmit data outputs to be routed internally back to the clock and data recovery circuit associated with each channel. When configured for local loopback, the associated transmit serial driver outputs are forced to output a differential

Signal Detect/Link Fault

Each selected line receiver (that is routed to the clock and data recovery PLL) is simultaneously monitored for:

■Analog amplitude above amplitude level selected by SDASELx

■Transition density above the specified limit

■Range controls report the received data stream inside normal frequency range (±1500 ppm)

■Receive channel enabled

■The presence of a reference clock

■ULCx is not asserted.

All of these conditions must be valid for the signal detect block to indicate a valid signal is present. This status is presented on the LFIx (Link Fault Indicator) output associated with each receive channel, which changes synchronous to the selected receive interface clock.

Analog Amplitude

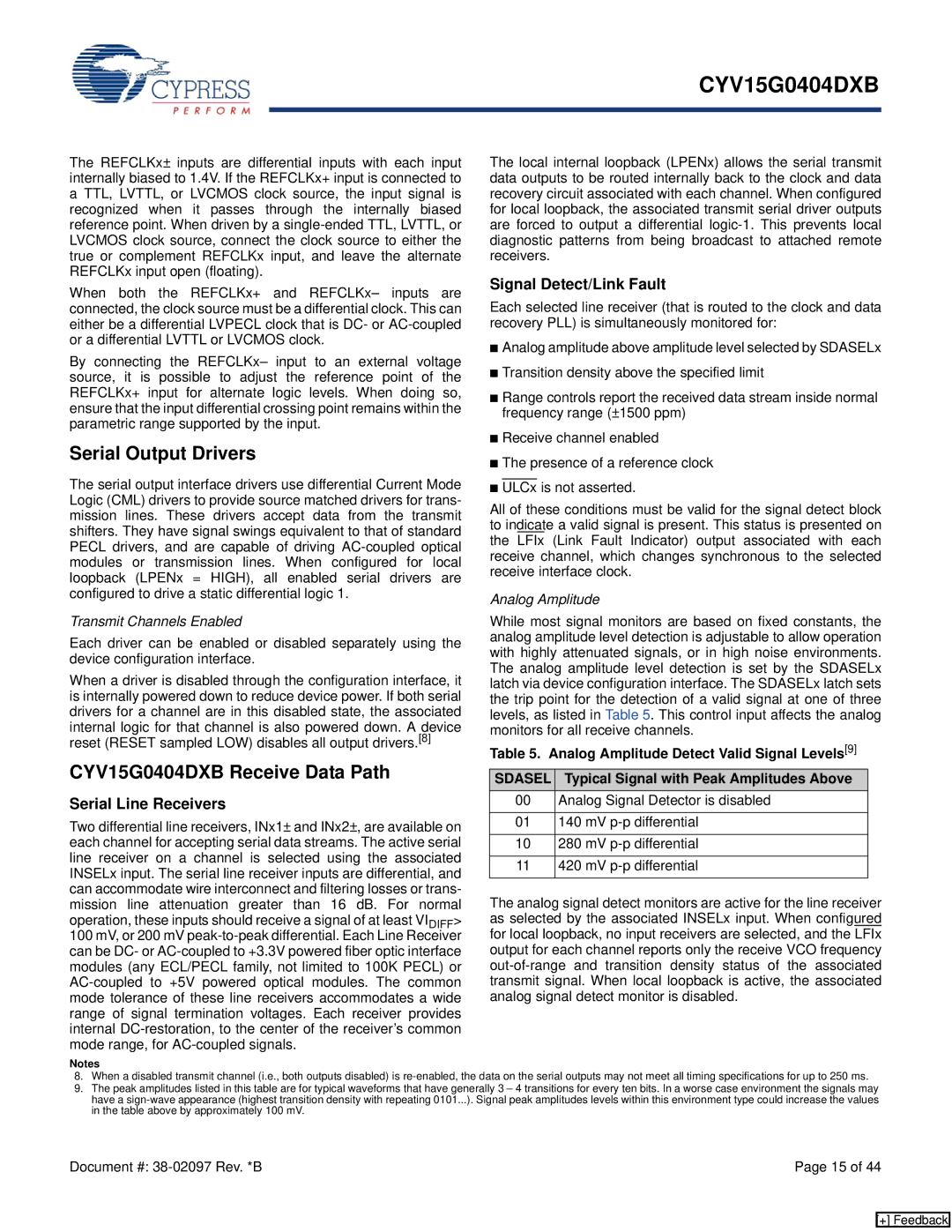

While most signal monitors are based on fixed constants, the analog amplitude level detection is adjustable to allow operation with highly attenuated signals, or in high noise environments. The analog amplitude level detection is set by the SDASELx latch via device configuration interface. The SDASELx latch sets the trip point for the detection of a valid signal at one of three levels, as listed in Table 5. This control input affects the analog monitors for all receive channels.

Table 5. Analog Amplitude Detect Valid Signal Levels[9]

SDASEL Typical Signal with Peak Amplitudes Above

00Analog Signal Detector is disabled

01140 mV

10280 mV

11420 mV

The analog signal detect monitors are active for the line receiver as selected by the associated INSELx input. When configured for local loopback, no input receivers are selected, and the LFIx output for each channel reports only the receive VCO frequency

8.When a disabled transmit channel (i.e., both outputs disabled) is

9.The peak amplitudes listed in this table are for typical waveforms that have generally 3 – 4 transitions for every ten bits. In a worse case environment the signals may have a

Document #: | Page 15 of 44 |

[+] Feedback