CYV15G0404DXB

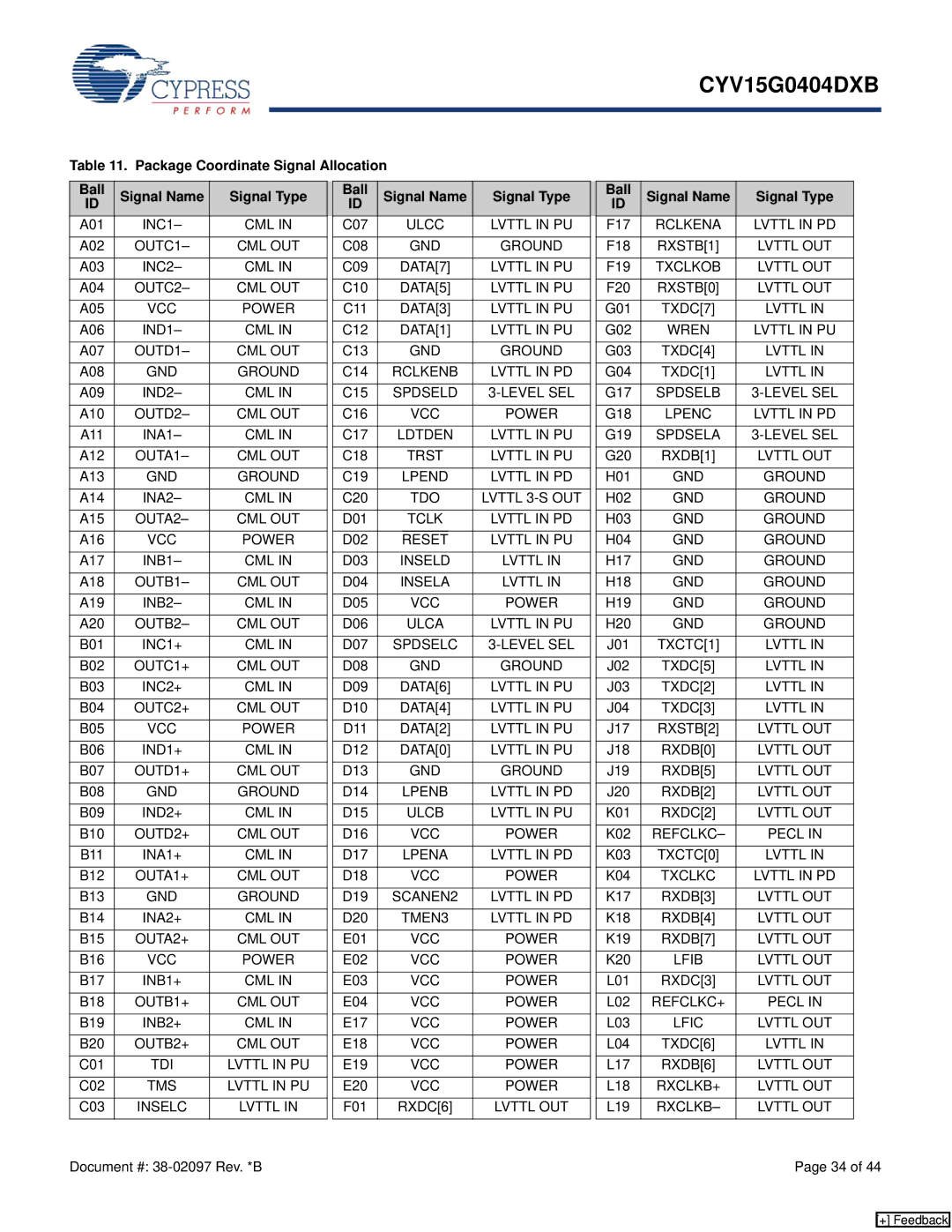

Table 11. Package Coordinate Signal Allocation

Ball | Signal Name | Signal Type | Ball | Signal Name | Signal Type | Ball | Signal Name | Signal Type |

| ||

ID |

|

| ID |

|

|

|

| ID |

|

|

|

A01 | INC1– | CML IN | C07 |

| ULCC | LVTTL IN PU | F17 | RCLKENA | LVTTL IN PD |

| |

|

|

|

|

|

|

|

|

|

|

| |

A02 | OUTC1– | CML OUT | C08 |

| GND | GROUND | F18 | RXSTB[1] | LVTTL OUT |

| |

|

|

|

|

|

|

|

|

|

| ||

A03 | INC2– | CML IN | C09 | DATA[7] | LVTTL IN PU | F19 | TXCLKOB | LVTTL OUT |

| ||

|

|

|

|

|

|

|

|

|

| ||

A04 | OUTC2– | CML OUT | C10 | DATA[5] | LVTTL IN PU | F20 | RXSTB[0] | LVTTL OUT |

| ||

|

|

|

|

|

|

|

|

|

| ||

A05 | VCC | POWER | C11 | DATA[3] | LVTTL IN PU | G01 | TXDC[7] | LVTTL IN |

| ||

|

|

|

|

|

|

|

|

|

| ||

A06 | IND1– | CML IN | C12 | DATA[1] | LVTTL IN PU | G02 | WREN | LVTTL IN PU |

| ||

|

|

|

|

|

|

|

|

|

|

| |

A07 | OUTD1– | CML OUT | C13 |

| GND | GROUND | G03 | TXDC[4] | LVTTL IN |

| |

|

|

|

|

|

|

|

|

|

| ||

A08 | GND | GROUND | C14 | RCLKENB | LVTTL IN PD | G04 | TXDC[1] | LVTTL IN |

| ||

|

|

|

|

|

|

|

|

|

| ||

A09 | IND2– | CML IN | C15 | SPDSELD |

| G17 | SPDSELB |

|

| ||

|

|

|

|

|

|

|

|

|

|

| |

A10 | OUTD2– | CML OUT | C16 |

| VCC | POWER | G18 | LPENC | LVTTL IN PD |

| |

|

|

|

|

|

|

|

|

|

| ||

A11 | INA1– | CML IN | C17 | LDTDEN | LVTTL IN PU | G19 | SPDSELA |

|

| ||

|

|

|

|

|

|

|

|

|

|

| |

A12 | OUTA1– | CML OUT | C18 |

| TRST | LVTTL IN PU | G20 | RXDB[1] | LVTTL OUT |

| |

|

|

|

|

|

|

|

|

|

| ||

A13 | GND | GROUND | C19 | LPEND | LVTTL IN PD | H01 | GND | GROUND |

| ||

|

|

|

|

|

|

|

|

|

|

| |

A14 | INA2– | CML IN | C20 |

| TDO | LVTTL | H02 | GND | GROUND |

| |

|

|

|

|

|

|

|

|

|

|

| |

A15 | OUTA2– | CML OUT | D01 |

| TCLK | LVTTL IN PD | H03 | GND | GROUND |

| |

|

|

|

|

|

|

|

|

|

|

|

|

A16 | VCC | POWER | D02 |

| RESET |

| LVTTL IN PU | H04 | GND | GROUND |

|

A17 | INB1– | CML IN | D03 | INSELD | LVTTL IN | H17 | GND | GROUND |

| ||

|

|

|

|

|

|

|

|

|

| ||

A18 | OUTB1– | CML OUT | D04 | INSELA | LVTTL IN | H18 | GND | GROUND |

| ||

|

|

|

|

|

|

|

|

|

|

| |

A19 | INB2– | CML IN | D05 |

| VCC | POWER | H19 | GND | GROUND |

| |

|

|

|

|

|

|

|

|

|

|

| |

A20 | OUTB2– | CML OUT | D06 |

| ULCA | LVTTL IN PU | H20 | GND | GROUND |

| |

|

|

|

|

|

|

|

|

|

| ||

B01 | INC1+ | CML IN | D07 | SPDSELC | J01 | TXCTC[1] | LVTTL IN |

| |||

|

|

|

|

|

|

|

|

|

|

| |

B02 | OUTC1+ | CML OUT | D08 |

| GND | GROUND | J02 | TXDC[5] | LVTTL IN |

| |

|

|

|

|

|

|

|

|

|

| ||

B03 | INC2+ | CML IN | D09 | DATA[6] | LVTTL IN PU | J03 | TXDC[2] | LVTTL IN |

| ||

|

|

|

|

|

|

|

|

|

| ||

B04 | OUTC2+ | CML OUT | D10 | DATA[4] | LVTTL IN PU | J04 | TXDC[3] | LVTTL IN |

| ||

|

|

|

|

|

|

|

|

|

| ||

B05 | VCC | POWER | D11 | DATA[2] | LVTTL IN PU | J17 | RXSTB[2] | LVTTL OUT |

| ||

|

|

|

|

|

|

|

|

|

| ||

B06 | IND1+ | CML IN | D12 | DATA[0] | LVTTL IN PU | J18 | RXDB[0] | LVTTL OUT |

| ||

|

|

|

|

|

|

|

|

|

|

| |

B07 | OUTD1+ | CML OUT | D13 |

| GND | GROUND | J19 | RXDB[5] | LVTTL OUT |

| |

|

|

|

|

|

|

|

|

|

|

| |

B08 | GND | GROUND | D14 |

| LPENB | LVTTL IN PD | J20 | RXDB[2] | LVTTL OUT |

| |

|

|

|

|

|

|

|

|

|

|

| |

B09 | IND2+ | CML IN | D15 |

| ULCB | LVTTL IN PU | K01 | RXDC[2] | LVTTL OUT |

| |

|

|

|

|

|

|

|

|

|

|

| |

B10 | OUTD2+ | CML OUT | D16 |

| VCC | POWER | K02 | REFCLKC– | PECL IN |

| |

|

|

|

|

|

|

|

|

|

|

| |

B11 | INA1+ | CML IN | D17 |

| LPENA | LVTTL IN PD | K03 | TXCTC[0] | LVTTL IN |

| |

|

|

|

|

|

|

|

|

|

|

| |

B12 | OUTA1+ | CML OUT | D18 |

| VCC | POWER | K04 | TXCLKC | LVTTL IN PD |

| |

|

|

|

|

|

|

|

|

|

| ||

B13 | GND | GROUND | D19 | SCANEN2 | LVTTL IN PD | K17 | RXDB[3] | LVTTL OUT |

| ||

|

|

|

|

|

|

|

|

|

| ||

B14 | INA2+ | CML IN | D20 | TMEN3 | LVTTL IN PD | K18 | RXDB[4] | LVTTL OUT |

| ||

|

|

|

|

|

|

|

|

|

|

| |

B15 | OUTA2+ | CML OUT | E01 |

| VCC | POWER | K19 | RXDB[7] | LVTTL OUT |

| |

|

|

|

|

|

|

|

|

|

|

| |

B16 | VCC | POWER | E02 |

| VCC | POWER | K20 | LFIB | LVTTL OUT |

| |

|

|

|

|

|

|

|

|

|

|

| |

B17 | INB1+ | CML IN | E03 |

| VCC | POWER | L01 | RXDC[3] | LVTTL OUT |

| |

|

|

|

|

|

|

|

|

|

|

| |

B18 | OUTB1+ | CML OUT | E04 |

| VCC | POWER | L02 | REFCLKC+ | PECL IN |

| |

|

|

|

|

|

|

|

|

|

|

| |

B19 | INB2+ | CML IN | E17 |

| VCC | POWER | L03 | LFIC | LVTTL OUT |

| |

|

|

|

|

|

|

|

|

|

|

| |

B20 | OUTB2+ | CML OUT | E18 |

| VCC | POWER | L04 | TXDC[6] | LVTTL IN |

| |

|

|

|

|

|

|

|

|

|

|

| |

C01 | TDI | LVTTL IN PU | E19 |

| VCC | POWER | L17 | RXDB[6] | LVTTL OUT |

| |

|

|

|

|

|

|

|

|

|

|

| |

C02 | TMS | LVTTL IN PU | E20 |

| VCC | POWER | L18 | RXCLKB+ | LVTTL OUT |

| |

|

|

|

|

|

|

|

|

|

| ||

C03 | INSELC | LVTTL IN | F01 | RXDC[6] | LVTTL OUT | L19 | RXCLKB– | LVTTL OUT |

| ||

|

|

|

|

|

|

|

|

|

|

|

|

Document #: |

|

|

|

|

|

|

| Page 34 of 44 | |||

[+] Feedback