CYV15G0404DXB

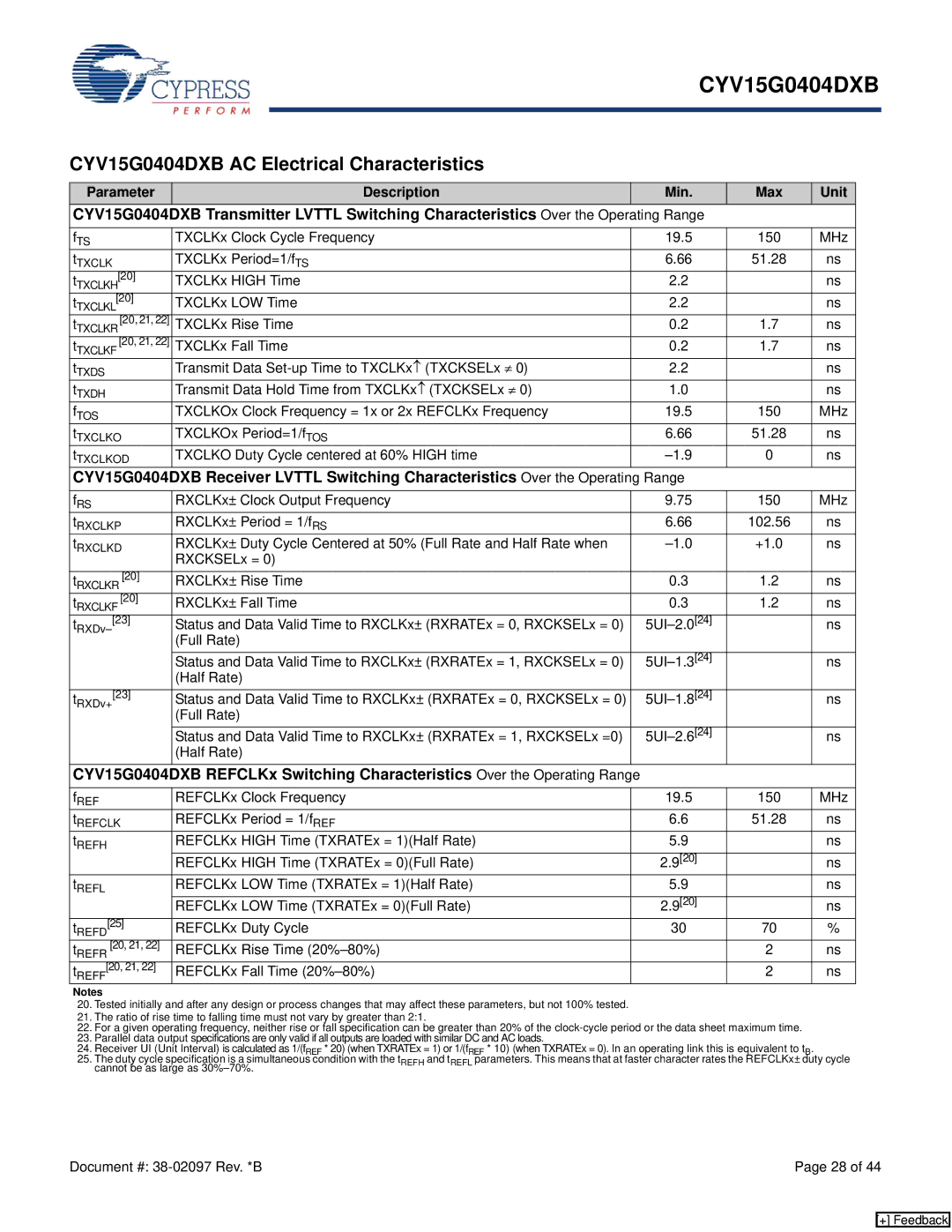

CYV15G0404DXB AC Electrical Characteristics

Parameter | Description | Min. | Max | Unit | ||

CYV15G0404DXB | Transmitter LVTTL Switching Characteristics Over the Operating Range |

|

| |||

fTS |

|

| TXCLKx Clock Cycle Frequency | 19.5 | 150 | MHz |

tTXCLK |

| TXCLKx Period=1/fTS | 6.66 | 51.28 | ns | |

tTXCLKH[20] | TXCLKx HIGH Time | 2.2 |

| ns | ||

tTXCLKL[20] | TXCLKx LOW Time | 2.2 |

| ns | ||

t |

| [20, 21, 22] | TXCLKx Rise Time | 0.2 | 1.7 | ns |

TXCLKR |

|

|

|

|

| |

t |

| [20, 21, 22] | TXCLKx Fall Time | 0.2 | 1.7 | ns |

TXCLKF |

|

|

|

|

| |

tTXDS |

|

| Transmit Data | 2.2 |

| ns |

tTXDH |

|

| Transmit Data Hold Time from TXCLKx↑ (TXCKSELx ≠ 0) | 1.0 |

| ns |

fTOS |

|

| TXCLKOx Clock Frequency = 1x or 2x REFCLKx Frequency | 19.5 | 150 | MHz |

tTXCLKO | TXCLKOx Period=1/fTOS | 6.66 | 51.28 | ns | ||

tTXCLKOD | TXCLKO Duty Cycle centered at 60% HIGH time | 0 | ns | |||

CYV15G0404DXB | Receiver LVTTL Switching Characteristics Over the Operating | Range |

|

| ||

fRS |

|

| RXCLKx± Clock Output Frequency | 9.75 | 150 | MHz |

tRXCLKP | RXCLKx± Period = 1/fRS | 6.66 | 102.56 | ns | ||

tRXCLKD | RXCLKx± Duty Cycle Centered at 50% (Full Rate and Half Rate when | +1.0 | ns | |||

|

|

| RXCKSELx = 0) |

|

|

|

tRXCLKR [20] | RXCLKx± Rise Time | 0.3 | 1.2 | ns | ||

tRXCLKF [20] | RXCLKx± Fall Time | 0.3 | 1.2 | ns | ||

t | [23] | Status and Data Valid Time to RXCLKx± (RXRATEx = 0, RXCKSELx = 0) |

| ns | ||

RXDv– |

|

| (Full Rate) |

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| Status and Data Valid Time to RXCLKx± (RXRATEx = 1, RXCKSELx = 0) |

| ns | |

|

|

| (Half Rate) |

|

|

|

t | [23] | Status and Data Valid Time to RXCLKx± (RXRATEx = 0, RXCKSELx = 0) |

| ns | ||

RXDv+ |

| (Full Rate) |

|

|

| |

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| Status and Data Valid Time to RXCLKx± (RXRATEx = 1, RXCKSELx =0) |

| ns | |

|

|

| (Half Rate) |

|

|

|

CYV15G0404DXB | REFCLKx Switching Characteristics Over the Operating Range |

|

|

| ||

fREF |

|

| REFCLKx Clock Frequency | 19.5 | 150 | MHz |

tREFCLK | REFCLKx Period = 1/fREF | 6.6 | 51.28 | ns | ||

tREFH |

|

| REFCLKx HIGH Time (TXRATEx = 1)(Half Rate) | 5.9 |

| ns |

|

|

| REFCLKx HIGH Time (TXRATEx = 0)(Full Rate) | 2.9[20] |

| ns |

tREFL |

|

| REFCLKx LOW Time (TXRATEx = 1)(Half Rate) | 5.9 |

| ns |

|

|

| REFCLKx LOW Time (TXRATEx = 0)(Full Rate) | 2.9[20] |

| ns |

tREFD[25] | REFCLKx Duty Cycle | 30 | 70 | % | ||

tREFR [20, 21, 22] | REFCLKx Rise Time |

| 2 | ns | ||

tREFF[20, 21, 22] | REFCLKx Fall Time |

| 2 | ns | ||

Notes

20.Tested initially and after any design or process changes that may affect these parameters, but not 100% tested.

21.The ratio of rise time to falling time must not vary by greater than 2:1.

22.For a given operating frequency, neither rise or fall specification can be greater than 20% of the

23.Parallel data output specifications are only valid if all outputs are loaded with similar DC and AC loads.

24.Receiver UI (Unit Interval) is calculated as 1/(fREF * 20) (when TXRATEx = 1) or 1/(fREF * 10) (when TXRATEx = 0). In an operating link this is equivalent to tB.

25.The duty cycle specification is a simultaneous condition with the tREFH and tREFL parameters. This means that at faster character rates the REFCLKx± duty cycle cannot be as large as

Document #: | Page 28 of 44 |

[+] Feedback