PCI-X Layout Guidelines

Note: PCI Express Assert_INTx/Deassert_INTx messages are not inhibited by the BME bit.

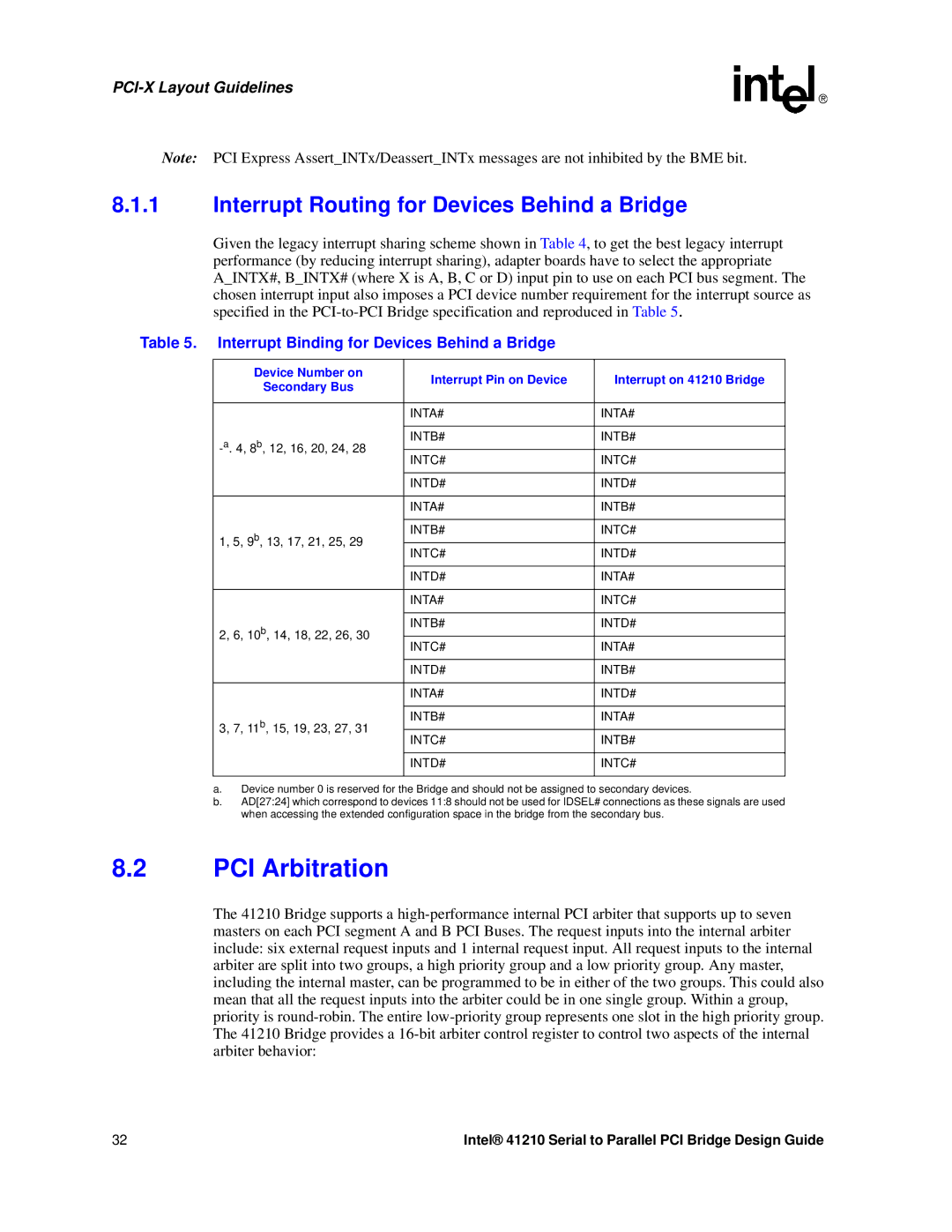

8.1.1Interrupt Routing for Devices Behind a Bridge

Given the legacy interrupt sharing scheme shown in Table 4, to get the best legacy interrupt performance (by reducing interrupt sharing), adapter boards have to select the appropriate A_INTX#, B_INTX# (where X is A, B, C or D) input pin to use on each PCI bus segment. The chosen interrupt input also imposes a PCI device number requirement for the interrupt source as specified in the

Table 5. Interrupt Binding for Devices Behind a Bridge

Device Number on | Interrupt Pin on Device | Interrupt on 41210 Bridge | |

Secondary Bus | |||

|

| ||

|

|

| |

| INTA# | INTA# | |

|

|

| |

INTB# | INTB# | ||

|

| ||

INTC# | INTC# | ||

| |||

|

|

| |

| INTD# | INTD# | |

|

|

| |

| INTA# | INTB# | |

|

|

| |

1, 5, 9b, 13, 17, 21, 25, 29 | INTB# | INTC# | |

|

| ||

INTC# | INTD# | ||

| |||

|

|

| |

| INTD# | INTA# | |

|

|

| |

| INTA# | INTC# | |

|

|

| |

2, 6, 10b, 14, 18, 22, 26, 30 | INTB# | INTD# | |

|

| ||

INTC# | INTA# | ||

| |||

|

|

| |

| INTD# | INTB# | |

|

|

| |

| INTA# | INTD# | |

|

|

| |

3, 7, 11b, 15, 19, 23, 27, 31 | INTB# | INTA# | |

|

| ||

INTC# | INTB# | ||

| |||

|

|

| |

| INTD# | INTC# | |

|

|

|

a.Device number 0 is reserved for the Bridge and should not be assigned to secondary devices.

b.AD[27:24] which correspond to devices 11:8 should not be used for IDSEL# connections as these signals are used when accessing the extended configuration space in the bridge from the secondary bus.

8.2PCI Arbitration

The 41210 Bridge supports a

32 | Intel® 41210 Serial to Parallel PCI Bridge Design Guide |