PCI-X Layout Guidelines

8.6.3PCI-X 66 MHz Embedded Topology

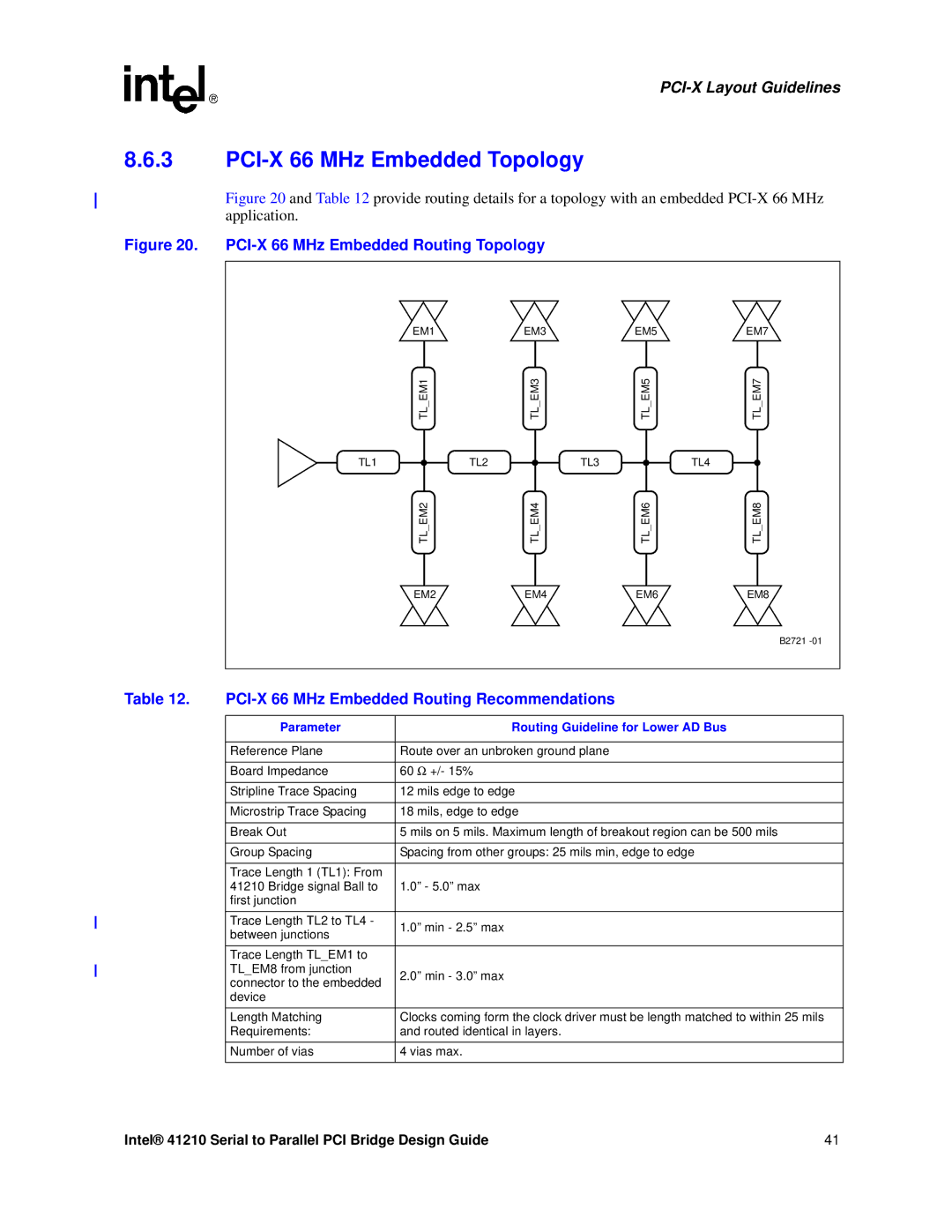

Figure 20 and Table 12 provide routing details for a topology with an embedded PCI-X 66 MHz application.

Figure 20. PCI-X 66 MHz Embedded Routing Topology

| EM1 | EM3 | EM5 | EM7 |

| TL EM1 | TL EM3 | TL EM5 | TL EM7 |

TL1 | TL2 | TL3 |

| TL4 |

| TL EM2 | TL EM4 | TL EM6 | TL EM8 |

| EM2 | EM4 | EM6 | EM8 |

|

|

|

| B2721 |

Table 12. |

| |

|

|

|

| Parameter | Routing Guideline for Lower AD Bus |

|

|

|

| Reference Plane | Route over an unbroken ground plane |

|

|

|

| Board Impedance | 60 Ω +/- 15% |

|

|

|

| Stripline Trace Spacing | 12 mils edge to edge |

|

|

|

| Microstrip Trace Spacing | 18 mils, edge to edge |

|

|

|

| Break Out | 5 mils on 5 mils. Maximum length of breakout region can be 500 mils |

|

|

|

| Group Spacing | Spacing from other groups: 25 mils min, edge to edge |

|

|

|

| Trace Length 1 (TL1): From |

|

| 41210 Bridge signal Ball to | 1.0” - 5.0” max |

| first junction |

|

|

|

|

| Trace Length TL2 to TL4 - | 1.0” min - 2.5” max |

| between junctions | |

|

| |

| Trace Length TL_EM1 to |

|

| TL_EM8 from junction | 2.0” min - 3.0” max |

| connector to the embedded | |

|

| |

| device |

|

|

|

|

| Length Matching | Clocks coming form the clock driver must be length matched to within 25 mils |

| Requirements: | and routed identical in layers. |

|

|

|

| Number of vias | 4 vias max. |

|

|

|

Intel® 41210 Serial to Parallel PCI Bridge Design Guide | 41 |