PCI Express Layout

9.2PCI-Express Layout Guidelines

The layout guidelines for

•

•Target Differential Impedance: 100 Ω +/- 20%.

•Driver Model: 41210 Bridge

•Receiver Model: 41210 Bridge

•Driver Package Model: Preliminary 41210 Bridge model.

•No receiver package model used since specification eye is at package pin.

•Assumed that traces in a lane could be routed totally on microstrip, totally on stripline, or a mixture of microstrip and stripline.

•AC coupling capacitors were modeled as a parasitic resistor and inductor in series.

•

•No vias were modeled at this time.

•Only the receiver eye was evaluated. The next revision will evaluate the eye at the transmitter and connector as well as the receiver.

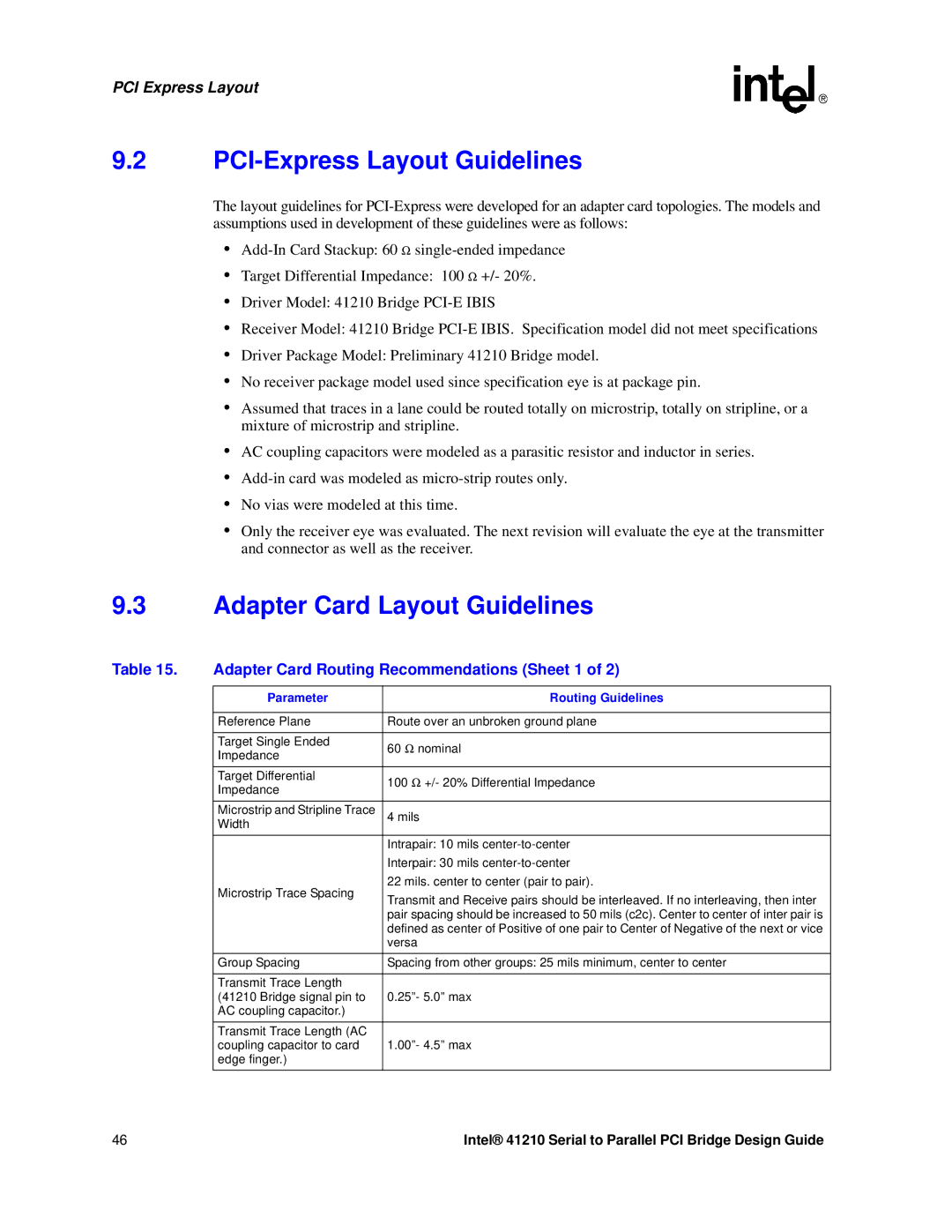

9.3Adapter Card Layout Guidelines

Table 15. | Adapter Card Routing Recommendations (Sheet 1 of 2) | |

|

|

|

| Parameter | Routing Guidelines |

|

|

|

| Reference Plane | Route over an unbroken ground plane |

|

|

|

| Target Single Ended | 60 Ω nominal |

| Impedance | |

|

| |

|

|

|

| Target Differential | 100 Ω +/- 20% Differential Impedance |

| Impedance | |

|

| |

| Microstrip and Stripline Trace | 4 mils |

| Width |

|

|

| Intrapair: 10 mils |

|

| Interpair: 30 mils |

| Microstrip Trace Spacing | 22 mils. center to center (pair to pair). |

| Transmit and Receive pairs should be interleaved. If no interleaving, then inter | |

|

| |

|

| pair spacing should be increased to 50 mils (c2c). Center to center of inter pair is |

|

| defined as center of Positive of one pair to Center of Negative of the next or vice |

|

| versa |

|

|

|

| Group Spacing | Spacing from other groups: 25 mils minimum, center to center |

|

|

|

| Transmit Trace Length |

|

| (41210 Bridge signal pin to | 0.25”- 5.0” max |

| AC coupling capacitor.) |

|

|

|

|

| Transmit Trace Length (AC |

|

| coupling capacitor to card | 1.00”- 4.5” max |

| edge finger.) |

|

|

|

|

46 | Intel® 41210 Serial to Parallel PCI Bridge Design Guide |