|

|

|

|

|

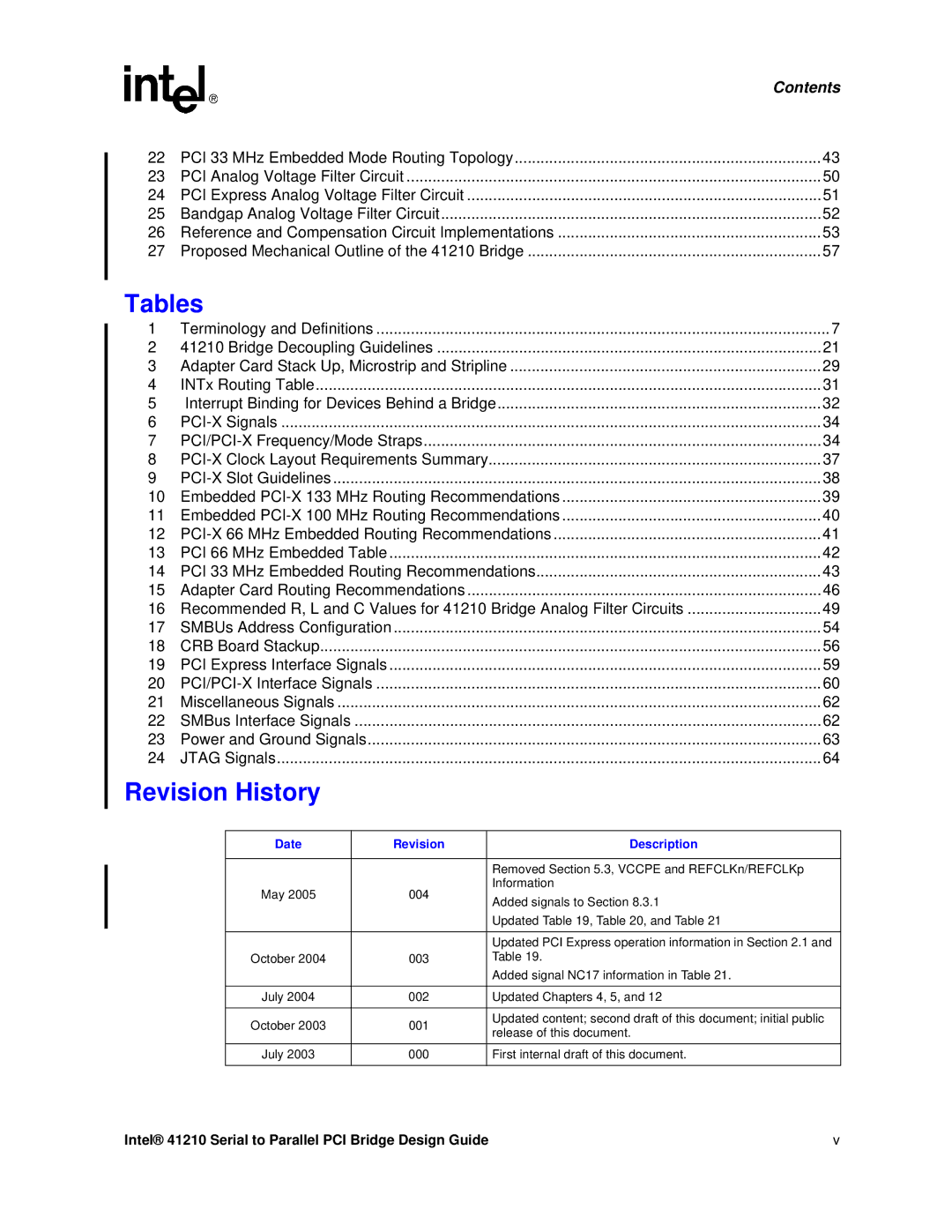

| Contents |

22 | PCI 33 MHz Embedded Mode Routing Topology | 43 | ||||

23 | PCI Analog Voltage Filter Circuit | 50 | ||||

24 | PCI Express Analog Voltage Filter Circuit | 51 | ||||

25 | Bandgap Analog Voltage Filter Circuit | 52 | ||||

26 | Reference and Compensation Circuit Implementations | 53 | ||||

27 | Proposed Mechanical Outline of the 41210 Bridge | 57 | ||||

Tables |

|

|

| |||

1 | Terminology and Definitions |

| 7 | |||

2 | 41210 Bridge Decoupling Guidelines | 21 | ||||

3 | Adapter Card Stack Up, Microstrip and Stripline | 29 | ||||

4 | INTx Routing Table |

| 31 | |||

5 | Interrupt Binding for Devices Behind a Bridge | 32 | ||||

6 |

| 34 | ||||

7 | 34 | |||||

8 |

| ............................................................................. | 37 | |||

9 |

| 38 | ||||

10 | Embedded | 39 | ||||

11 | Embedded | 40 | ||||

12 | 41 | |||||

13 | PCI 66 MHz Embedded Table |

| 42 | |||

14 | PCI 33 MHz Embedded Routing Recommendations | 43 | ||||

15 | Adapter Card Routing Recommendations | 46 | ||||

16 | Recommended R, L and C Values for 41210 Bridge Analog Filter Circuits | 49 | ||||

17 | SMBUs Address Configuration | ................................................................................................... |

| 54 | ||

18 | CRB Board Stackup |

| 56 | |||

19 | PCI Express Interface Signals |

| 59 | |||

20 |

| 60 | ||||

21 | Miscellaneous Signals |

| 62 | |||

22 | SMBus Interface Signals |

| 62 | |||

23 | Power and Ground Signals |

| 63 | |||

24 | JTAG Signals |

| 64 | |||

Revision History |

|

|

| |||

|

|

|

|

|

|

|

|

| Date |

| Revision | Description |

|

|

|

|

|

|

| |

|

|

|

|

| Removed Section 5.3, VCCPE and REFCLKn/REFCLKp | |

|

| May 2005 |

| 004 | Information |

|

|

|

| Added signals to Section 8.3.1 |

| ||

|

|

|

|

|

| |

|

|

|

|

| Updated Table 19, Table 20, and Table 21 |

|

|

|

|

|

|

| |

|

|

|

|

| Updated PCI Express operation information in Section 2.1 and | |

|

| October 2004 |

| 003 | Table 19. |

|

|

|

|

|

| Added signal NC17 information in Table 21. |

|

|

|

|

|

|

|

|

|

| July 2004 |

| 002 | Updated Chapters 4, 5, and 12 |

|

|

|

|

|

|

| |

|

| October 2003 |

| 001 | Updated content; second draft of this document; initial public | |

|

|

| release of this document. |

| ||

|

|

|

|

|

| |

|

| July 2003 |

| 000 | First internal draft of this document. |

|

|

|

|

|

|

|

|

Intel® 41210 Serial to Parallel PCI Bridge Design Guide | v |