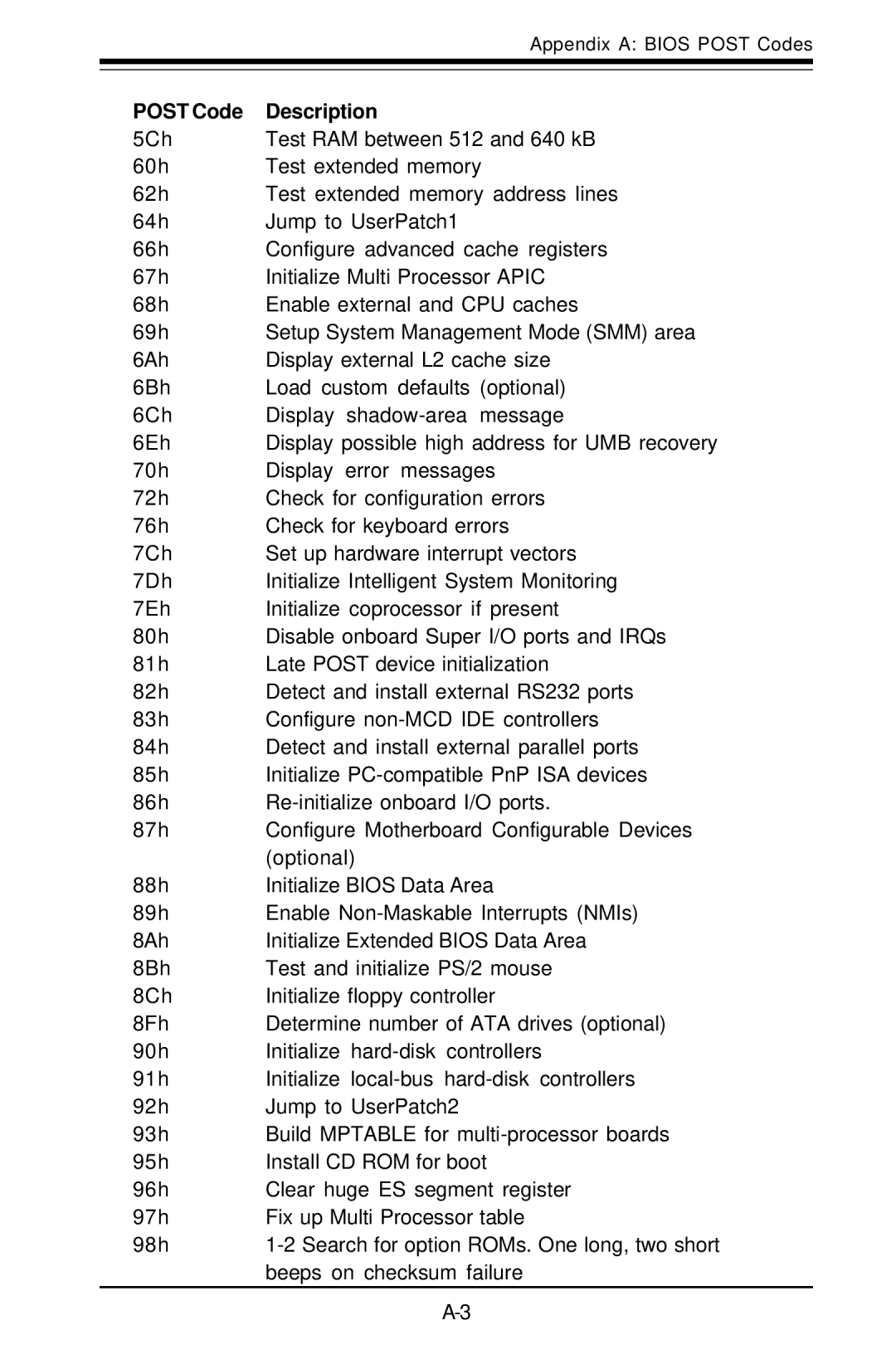

| Appendix A: BIOS POST Codes |

|

|

POST Code | Description |

5Ch | Test RAM between 512 and 640 kB |

60h | Test extended memory |

62h | Test extended memory address lines |

64h | Jump to UserPatch1 |

66h | Configure advanced cache registers |

67h | Initialize Multi Processor APIC |

68h | Enable external and CPU caches |

69h | Setup System Management Mode (SMM) area |

6Ah | Display external L2 cache size |

6Bh | Load custom defaults (optional) |

6Ch | Display |

6Eh | Display possible high address for UMB recovery |

70h | Display error messages |

72h | Check for configuration errors |

76h | Check for keyboard errors |

7Ch | Set up hardware interrupt vectors |

7Dh | Initialize Intelligent System Monitoring |

7Eh | Initialize coprocessor if present |

80h | Disable onboard Super I/O ports and IRQs |

81h | Late POST device initialization |

82h | Detect and install external RS232 ports |

83h | Configure |

84h | Detect and install external parallel ports |

85h | Initialize |

86h | |

87h | Configure Motherboard Configurable Devices |

| (optional) |

88h | Initialize BIOS Data Area |

89h | Enable |

8Ah | Initialize Extended BIOS Data Area |

8Bh | Test and initialize PS/2 mouse |

8Ch | Initialize floppy controller |

8Fh | Determine number of ATA drives (optional) |

90h | Initialize |

91h | Initialize |

92h | Jump to UserPatch2 |

93h | Build MPTABLE for |

95h | Install CD ROM for boot |

96h | Clear huge ES segment register |

97h | Fix up Multi Processor table |

98h | |

| beeps on checksum failure |

|

Page 99

Image 99