Peripheral Architecture | www.ti.com |

2.2Clock Generation

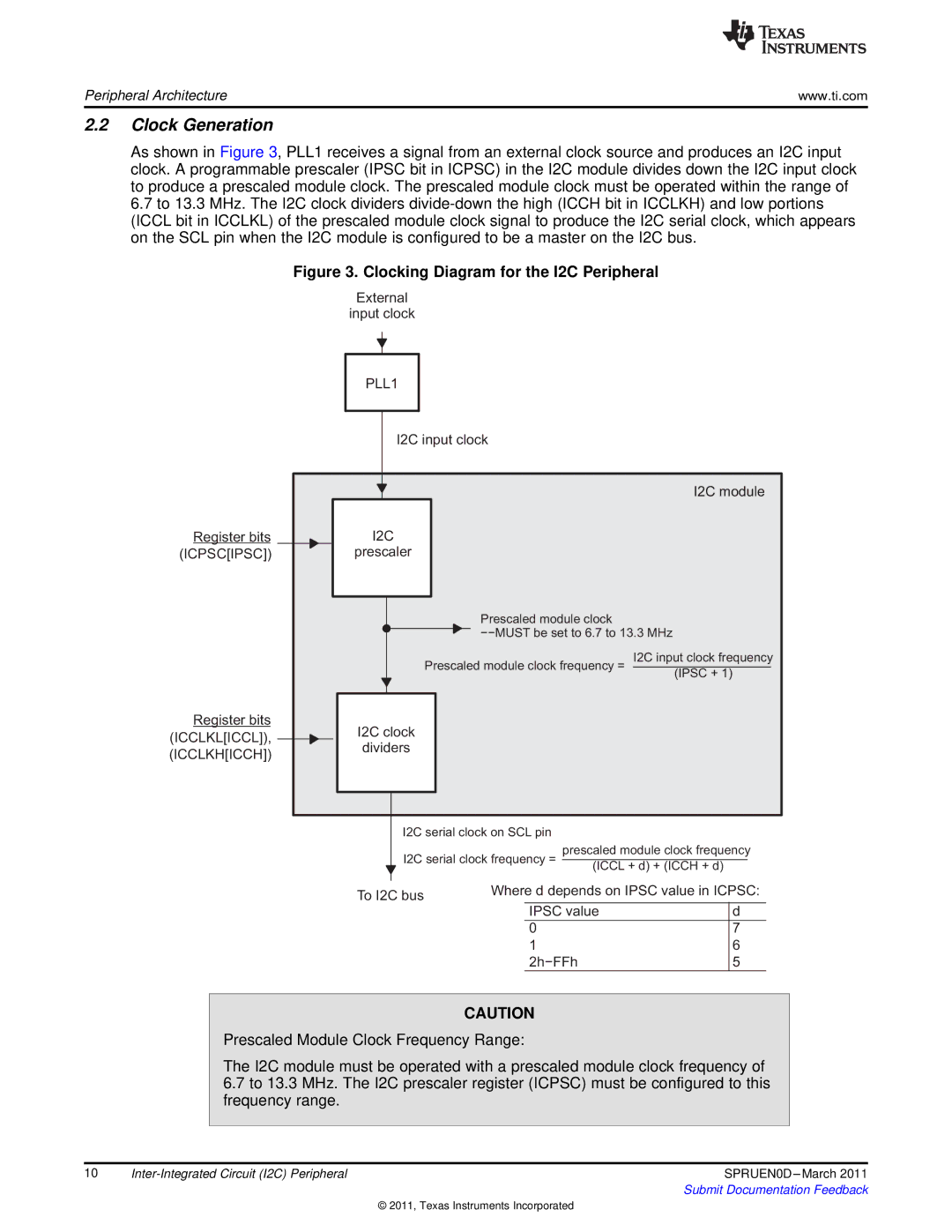

As shown in Figure 3, PLL1 receives a signal from an external clock source and produces an I2C input clock. A programmable prescaler (IPSC bit in ICPSC) in the I2C module divides down the I2C input clock to produce a prescaled module clock. The prescaled module clock must be operated within the range of 6.7 to 13.3 MHz. The I2C clock dividers

Figure 3. Clocking Diagram for the I2C Peripheral

External

input clock

Register bits (ICPSC[IPSC])

Register bits (ICCLKL[ICCL]), (ICCLKH[ICCH])

PLL1

I2C input clock

I2C module

I2C

prescaler

Prescaled module clock

−−MUST be set to 6.7 to 13.3 MHz

Prescaled module clock frequency = I2C input clock frequency (IPSC + 1)

I2C clock

dividers

I2C serial clock on SCL pin

I2C serial clock frequency = prescaled module clock frequency (ICCL + d) + (ICCH + d)

To I2C bus | Where d depends on IPSC value in ICPSC: | ||

|

|

| |

|

| IPSC value | d |

|

|

|

|

| 0 | 7 | |

| 1 | 6 | |

|

| 2h−FFh | 5 |

CAUTION

Prescaled Module Clock Frequency Range:

The I2C module must be operated with a prescaled module clock frequency of

6.7to 13.3 MHz. The I2C prescaler register (ICPSC) must be configured to this frequency range.

10 | SPRUEN0D | |

|

| Submit Documentation Feedback |

© 2011, Texas Instruments Incorporated