www.ti.comRegisters

Table 16. How the MST and FDF Bits Affect the Role of TRX Bit

ICMDR Bit |

|

| |

MST | FDF | I2C State | Function of TRX Bit |

|

|

|

|

0 | 0 | In slave mode but not free data format | TRX is a don't care. Depending on the command from the master, the I2C |

|

| mode | responds as a receiver or a transmitter. |

0 | 1 | In slave mode and free data format | The free data format mode requires that the transmitter and receiver be |

|

| mode | fixed. TRX identifies the role of the I2C: |

TRX = 0: The I2C is a receiver.

TRX = 1: The I2C is a transmitter.

10 In master mode but not free data format mode

TRX identifies the role of the I2C:

TRX = 0: The I2C is a receiver.

TRX = 1: The I2C is a transmitter.

1 | 1 | In master mode and free data format | The free data format mode requires that the transmitter and receiver be |

|

| mode | fixed. TRX identifies the role of the I2C: |

TRX = 0: The I2C is a receiver.

TRX = 1: The I2C is a transmitter.

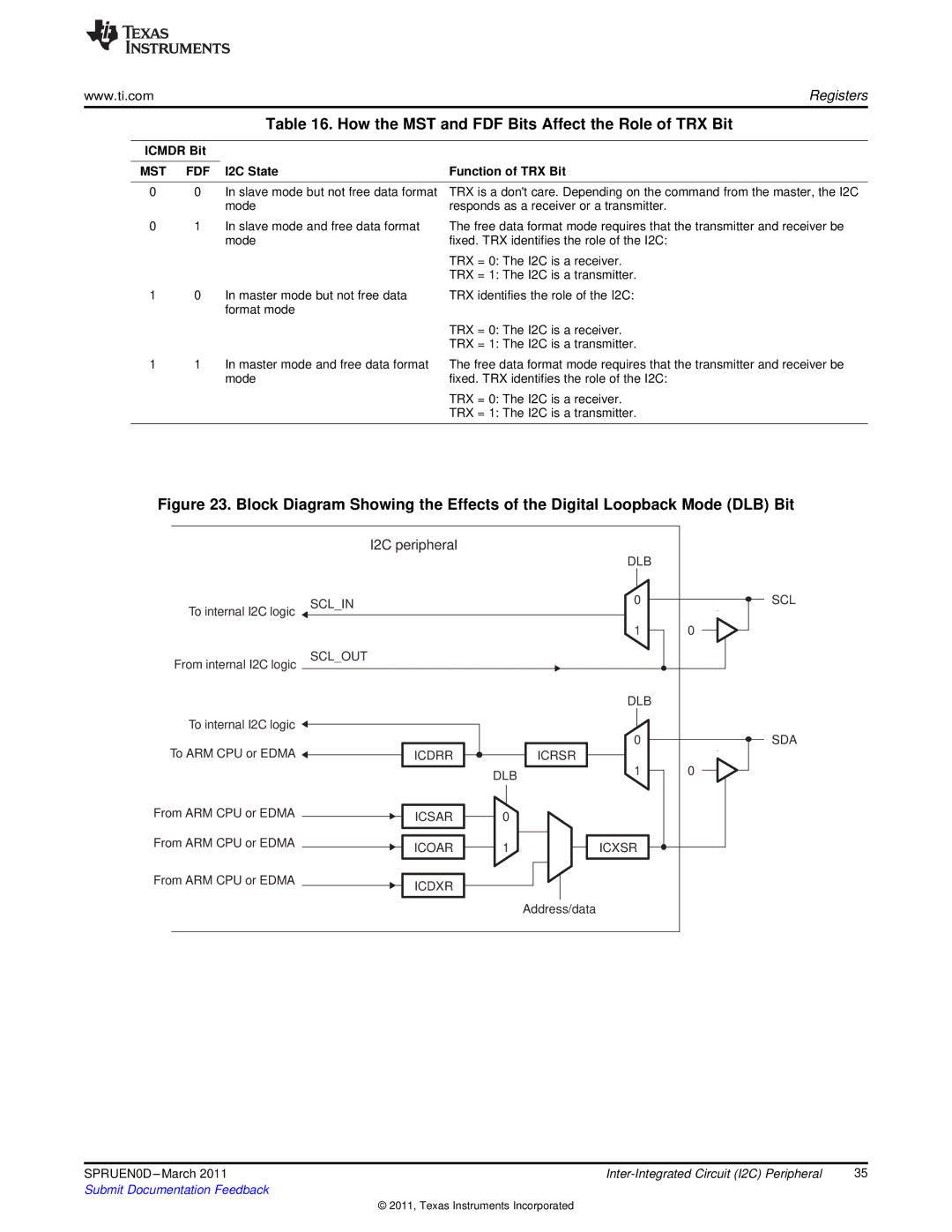

Figure 23. Block Diagram Showing the Effects of the Digital Loopback Mode (DLB) Bit

| I2C peripheral |

|

|

|

|

|

| DLB |

|

To internal I2C logic | SCL_IN |

| 0 | SCL |

|

|

| ||

|

|

|

| |

|

|

| 1 | 0 |

From internal I2C logic | SCL_OUT |

|

|

|

|

|

|

| |

|

|

| DLB |

|

To internal I2C logic |

|

|

|

|

To ARM CPU or EDMA |

|

| 0 | SDA |

ICDRR |

| ICRSR |

| |

|

| DLB | 1 | 0 |

|

|

|

| |

From ARM CPU or EDMA | ICSAR | 0 |

|

|

|

|

| ||

From ARM CPU or EDMA | ICOAR | 1 | ICXSR |

|

|

| |||

From ARM CPU or EDMA | ICDXR |

|

|

|

|

|

|

| |

|

|

| Address/data |

|

SPRUEN0D | 35 | |

Submit Documentation Feedback |

|

|

© 2011, Texas Instruments Incorporated