www.ti.com | Registers |

3.8I2C Data Transmit Register (ICDXR)

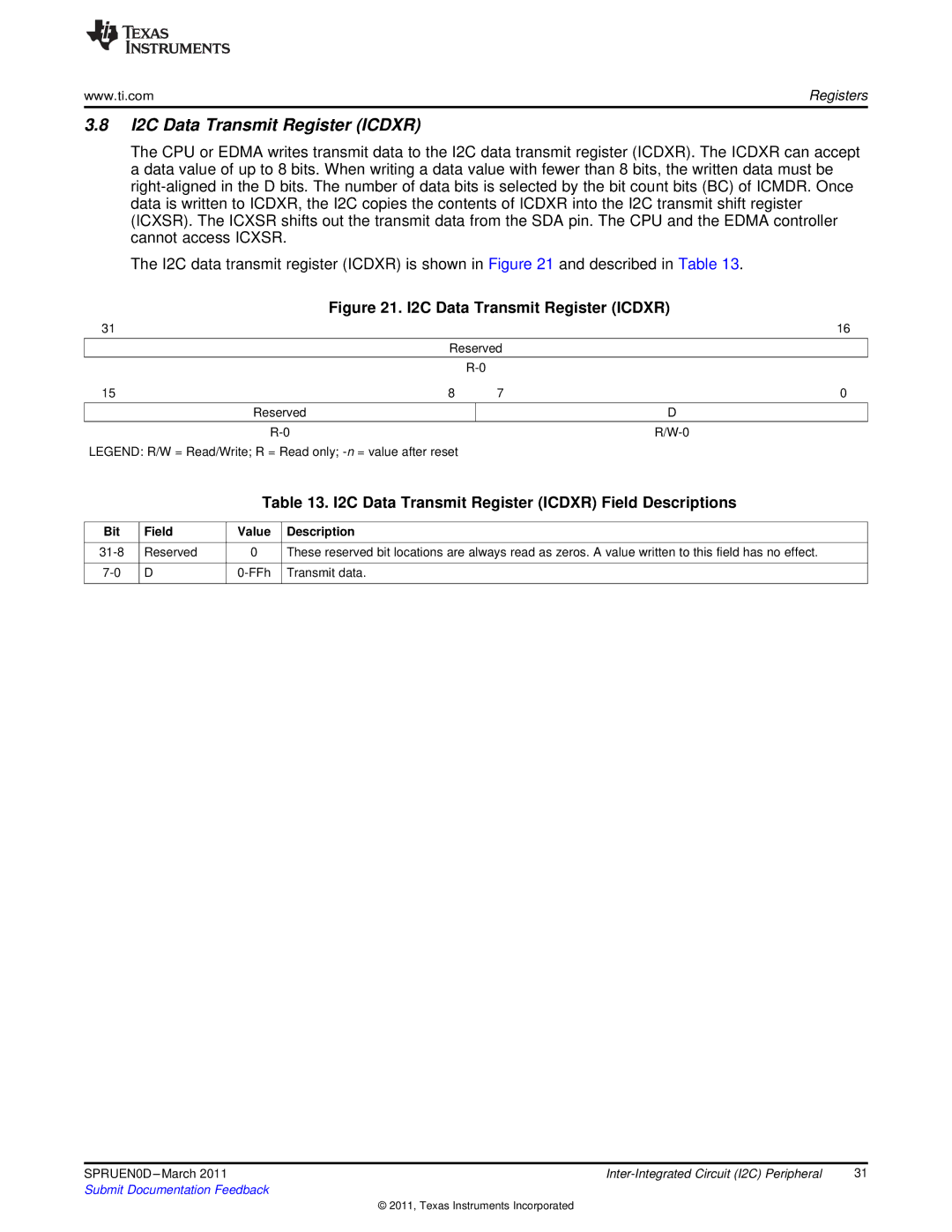

The CPU or EDMA writes transmit data to the I2C data transmit register (ICDXR). The ICDXR can accept a data value of up to 8 bits. When writing a data value with fewer than 8 bits, the written data must be

The I2C data transmit register (ICDXR) is shown in Figure 21 and described in Table 13.

Figure 21. I2C Data Transmit Register (ICDXR)

31 |

|

|

| 16 |

| Reserved |

| ||

|

|

|

| |

|

|

| ||

15 | 8 | 7 | 0 | |

|

|

|

|

|

| Reserved |

|

| D |

|

|

|

|

|

|

|

| ||

LEGEND: R/W = Read/Write; R = Read only;

Table 13. I2C Data Transmit Register (ICDXR) Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

Reserved | 0 | These reserved bit locations are always read as zeros. A value written to this field has no effect. | |

|

|

|

|

D | Transmit data. | ||

|

|

|

|

SPRUEN0D | 31 | |

Submit Documentation Feedback |

|

|

© 2011, Texas Instruments Incorporated