www.ti.com | Peripheral Architecture |

2.7Endianness Considerations

When the device is configured for

•

•

•

In general, software programs the CPU to use

No offset is needed to access the I2C registers when the device is configured in

2.8Operating Modes

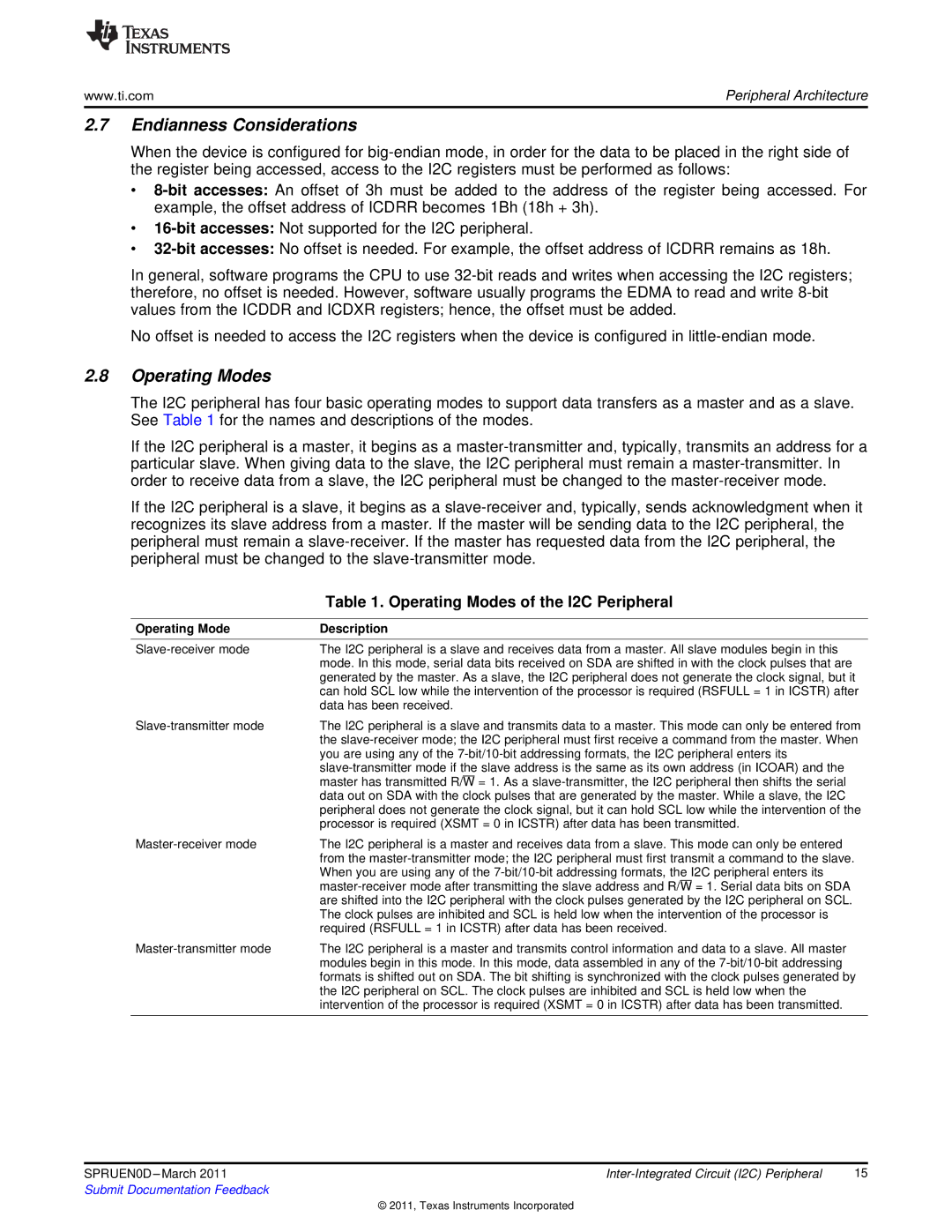

The I2C peripheral has four basic operating modes to support data transfers as a master and as a slave. See Table 1 for the names and descriptions of the modes.

If the I2C peripheral is a master, it begins as a

If the I2C peripheral is a slave, it begins as a

| Table 1. Operating Modes of the I2C Peripheral | ||||

|

| ||||

Operating Mode | Description | ||||

|

| ||||

The I2C peripheral is a slave and receives data from a master. All slave modules begin in this | |||||

| mode. In this mode, serial data bits received on SDA are shifted in with the clock pulses that are | ||||

| generated by the master. As a slave, the I2C peripheral does not generate the clock signal, but it | ||||

| can hold SCL low while the intervention of the processor is required (RSFULL = 1 in ICSTR) after | ||||

| data has been received. | ||||

The I2C peripheral is a slave and transmits data to a master. This mode can only be entered from | |||||

| the | ||||

| you are using any of the | ||||

| |||||

|

|

| = 1. As a | ||

| master has transmitted R/W | ||||

| data out on SDA with the clock pulses that are generated by the master. While a slave, the I2C | ||||

| peripheral does not generate the clock signal, but it can hold SCL low while the intervention of the | ||||

| processor is required (XSMT = 0 in ICSTR) after data has been transmitted. | ||||

The I2C peripheral is a master and receives data from a slave. This mode can only be entered | |||||

| from the | ||||

| When you are using any of the | ||||

|

|

|

|

| = 1. Serial data bits on SDA |

| |||||

| are shifted into the I2C peripheral with the clock pulses generated by the I2C peripheral on SCL. | ||||

| The clock pulses are inhibited and SCL is held low when the intervention of the processor is | ||||

| required (RSFULL = 1 in ICSTR) after data has been received. | ||||

The I2C peripheral is a master and transmits control information and data to a slave. All master | |||||

| modules begin in this mode. In this mode, data assembled in any of the | ||||

| formats is shifted out on SDA. The bit shifting is synchronized with the clock pulses generated by | ||||

| the I2C peripheral on SCL. The clock pulses are inhibited and SCL is held low when the | ||||

| intervention of the processor is required (XSMT = 0 in ICSTR) after data has been transmitted. | ||||

|

|

|

|

|

|

SPRUEN0D | 15 | |

Submit Documentation Feedback |

|

|

© 2011, Texas Instruments Incorporated