Registers | www.ti.com |

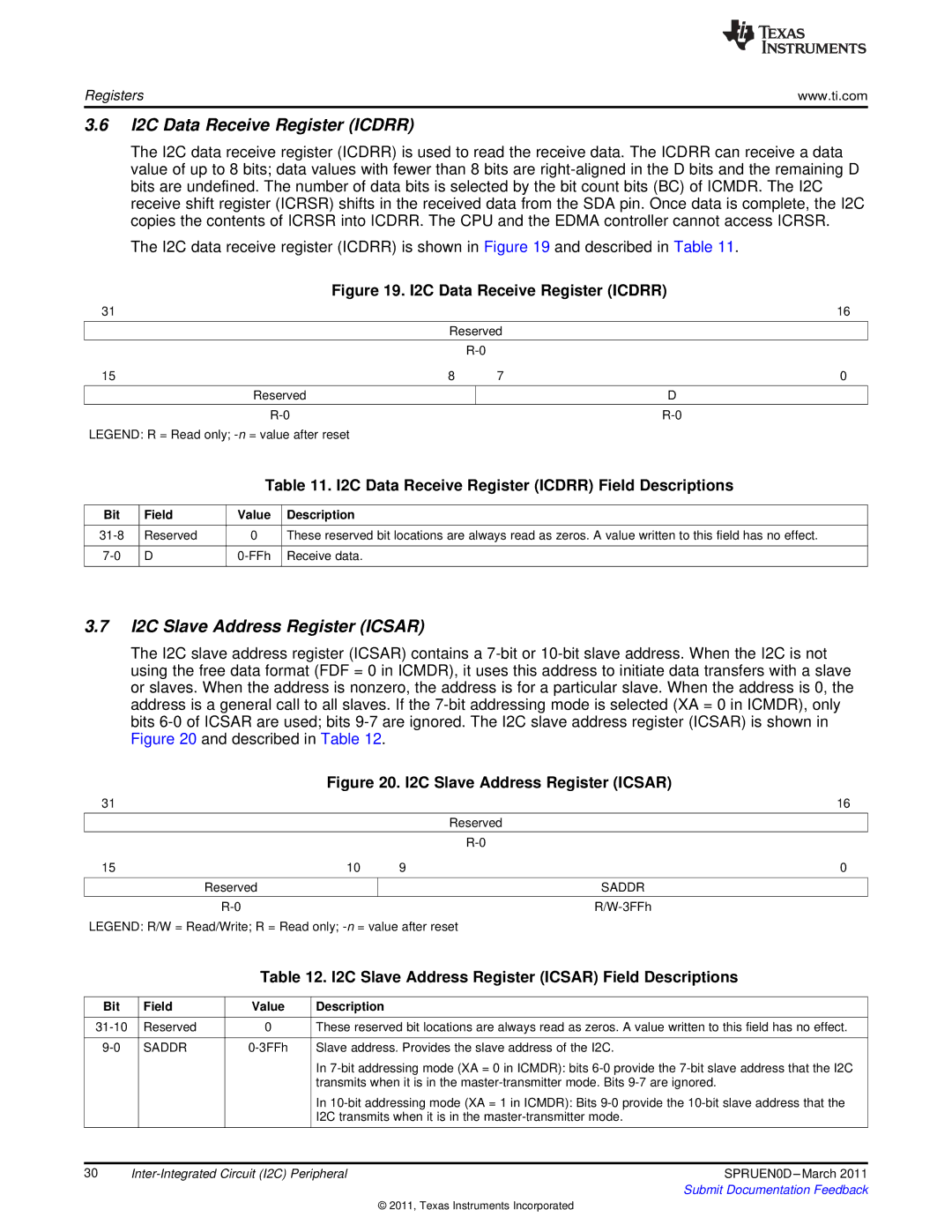

3.6I2C Data Receive Register (ICDRR)

The I2C data receive register (ICDRR) is used to read the receive data. The ICDRR can receive a data value of up to 8 bits; data values with fewer than 8 bits are

The I2C data receive register (ICDRR) is shown in Figure 19 and described in Table 11.

Figure 19. I2C Data Receive Register (ICDRR)

31 |

|

|

| 16 |

| Reserved |

| ||

|

|

| ||

15 | 8 | 7 | 0 | |

|

|

|

|

|

| Reserved |

|

| D |

|

|

| ||

LEGEND: R = Read only;

Table 11. I2C Data Receive Register (ICDRR) Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

Reserved | 0 | These reserved bit locations are always read as zeros. A value written to this field has no effect. | |

|

|

|

|

D | Receive data. | ||

|

|

|

|

3.7I2C Slave Address Register (ICSAR)

The I2C slave address register (ICSAR) contains a

Figure 20. I2C Slave Address Register (ICSAR)

31 |

|

| 16 |

|

|

| Reserved |

|

|

|

|

|

|

| |

15 | 10 | 9 | 0 |

|

|

|

|

| Reserved |

| SADDR |

|

|

|

|

|

|

LEGEND: R/W = Read/Write; R = Read only;

Table 12. I2C Slave Address Register (ICSAR) Field Descriptions

Bit |

| Field | Value | Description |

|

|

|

|

|

| |

| Reserved | 0 | These reserved bit locations are always read as zeros. A value written to this field has no effect. | ||

|

|

|

|

|

|

| SADDR | Slave address. Provides the slave address of the I2C. |

| ||

|

|

|

| In | |

|

|

|

| transmits when it is in the | |

|

|

|

| In | |

|

|

|

| I2C transmits when it is in the |

|

|

|

|

|

|

|

|

|

|

|

|

|

30 | SPRUEN0D | ||||

|

|

|

|

| Submit Documentation Feedback |

© 2011, Texas Instruments Incorporated