Introduction | www.ti.com |

1.3Functional Block Diagram

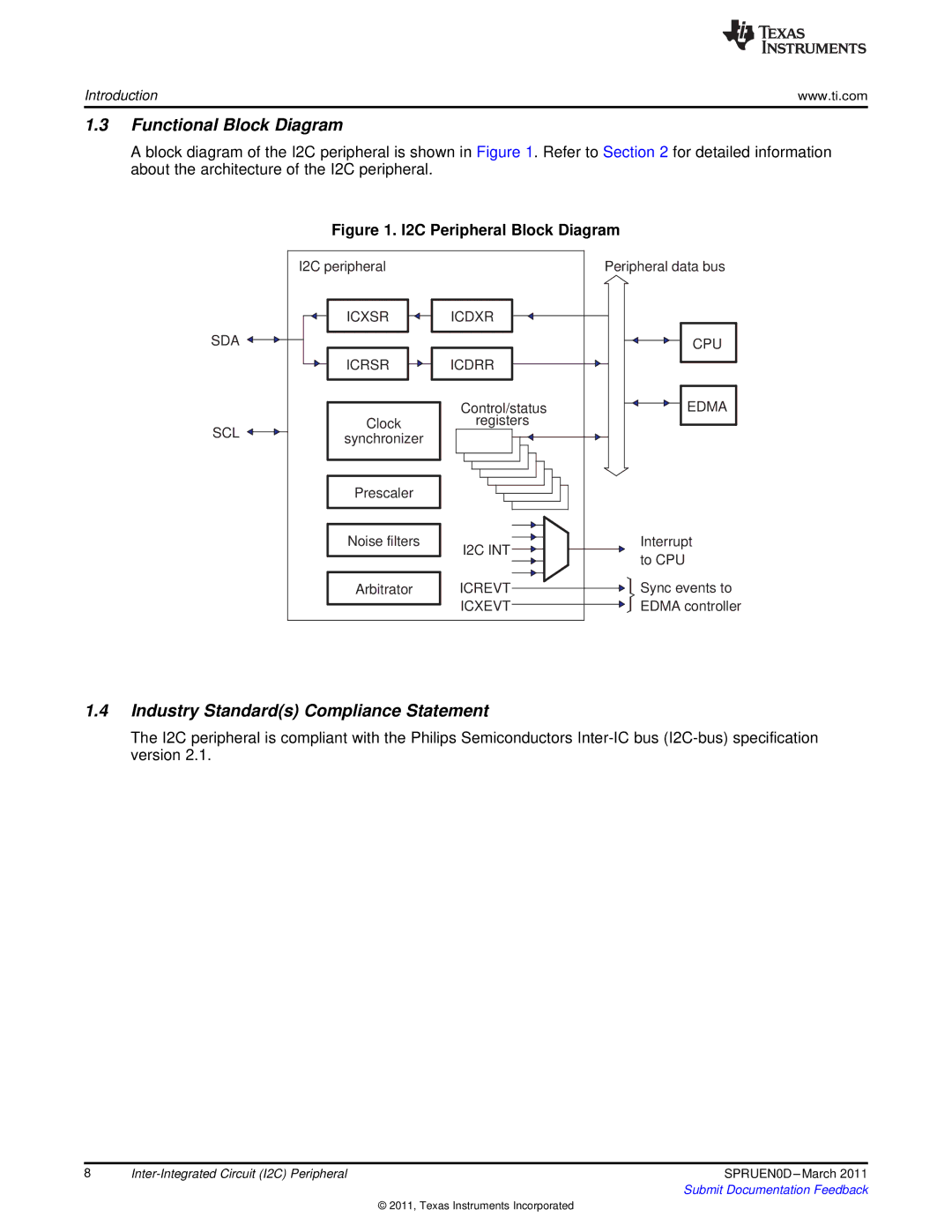

A block diagram of the I2C peripheral is shown in Figure 1. Refer to Section 2 for detailed information about the architecture of the I2C peripheral.

Figure 1. I2C Peripheral Block Diagram

| I2C peripheral |

| Peripheral data bus |

| ICXSR | ICDXR |

|

SDA |

|

| CPU |

| ICRSR | ICDRR |

|

|

| Control/status | EDMA |

SCL | Clock | registers |

|

synchronizer |

|

| |

|

|

| |

| Prescaler |

|

|

| Noise filters | I2C INT | Interrupt |

|

| to CPU | |

|

|

| |

| Arbitrator | ICREVT | Sync events to |

|

| ICXEVT | EDMA controller |

1.4Industry Standard(s) Compliance Statement

The I2C peripheral is compliant with the Philips Semiconductors

8 | SPRUEN0D |

Submit Documentation Feedback

© 2011, Texas Instruments Incorporated