Registers | www.ti.com |

3.10 I2C Interrupt Vector Register (ICIVR)

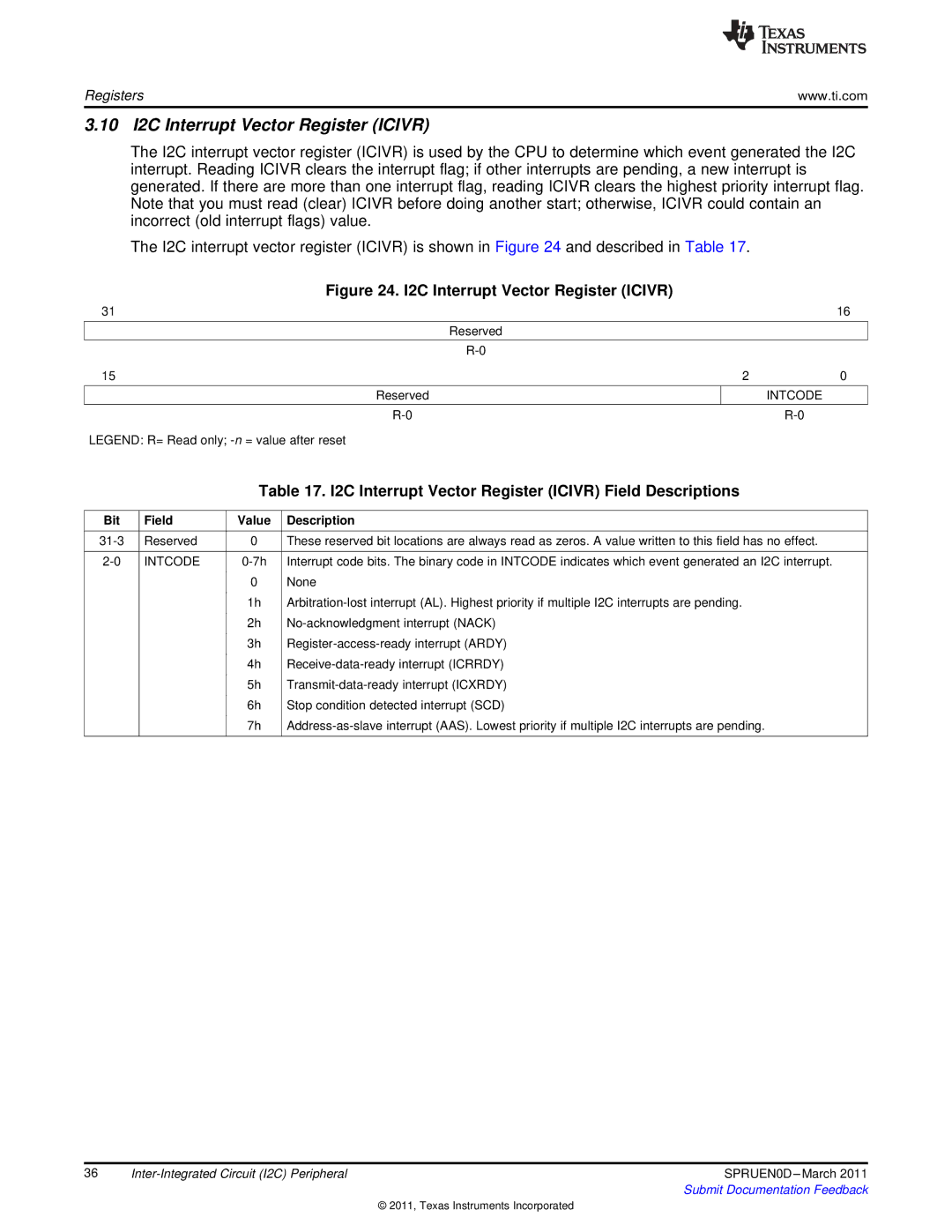

The I2C interrupt vector register (ICIVR) is used by the CPU to determine which event generated the I2C interrupt. Reading ICIVR clears the interrupt flag; if other interrupts are pending, a new interrupt is generated. If there are more than one interrupt flag, reading ICIVR clears the highest priority interrupt flag. Note that you must read (clear) ICIVR before doing another start; otherwise, ICIVR could contain an incorrect (old interrupt flags) value.

The I2C interrupt vector register (ICIVR) is shown in Figure 24 and described in Table 17.

Figure 24. I2C Interrupt Vector Register (ICIVR)

31 | 16 |

Reserved

15

Reserved

LEGEND: R= Read only;

20

INTCODE

Table 17. I2C Interrupt Vector Register (ICIVR) Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

Reserved | 0 | These reserved bit locations are always read as zeros. A value written to this field has no effect. | |

|

|

|

|

INTCODE | Interrupt code bits. The binary code in INTCODE indicates which event generated an I2C interrupt. | ||

|

| 0 | None |

|

| 1h | |

|

| 2h | |

|

| 3h | |

|

| 4h | |

|

| 5h | |

|

| 6h | Stop condition detected interrupt (SCD) |

|

| 7h | |

|

|

|

|

36 | SPRUEN0D | |

|

| Submit Documentation Feedback |

© 2011, Texas Instruments Incorporated