www.ti.com | Registers |

3.3I2C Interrupt Status Register (ICSTR)

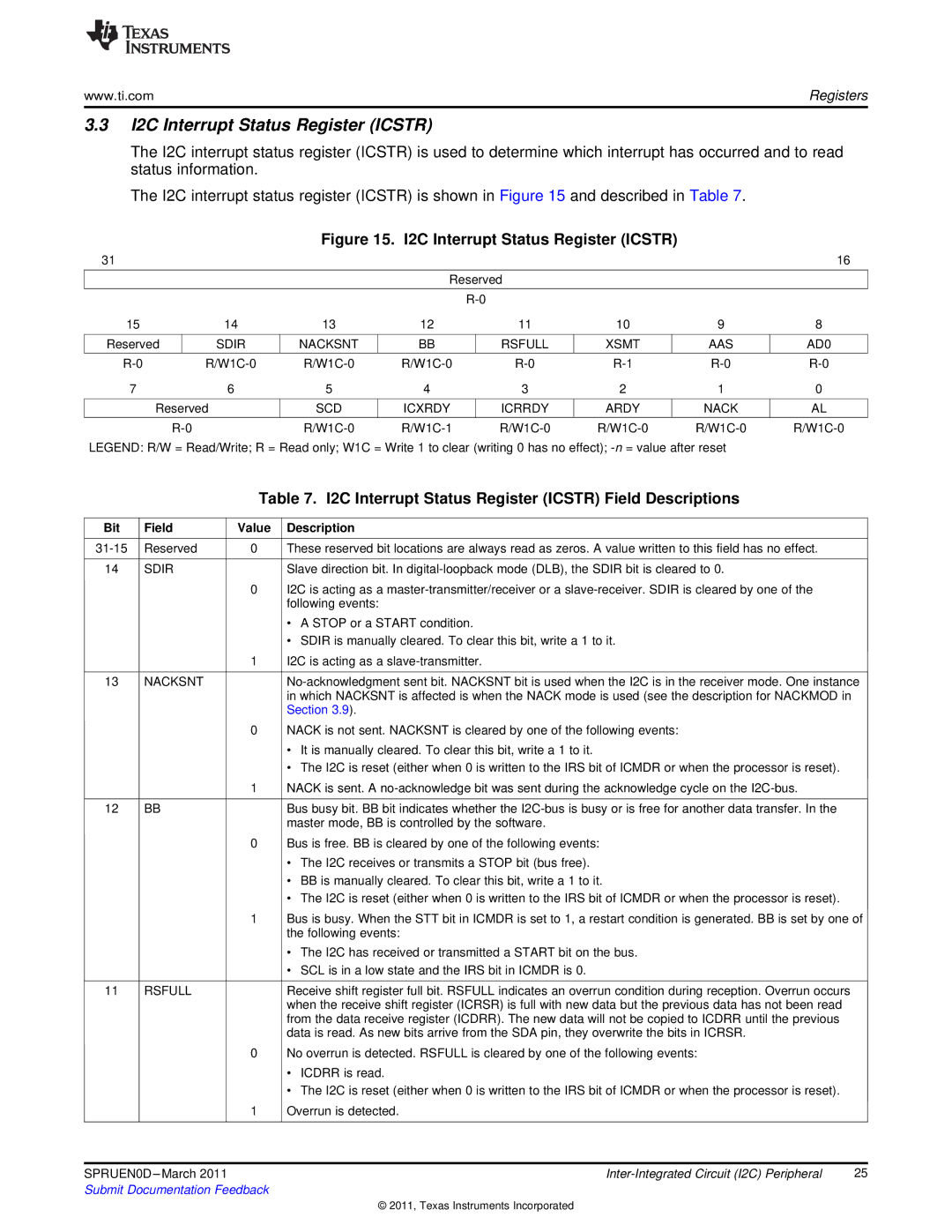

The I2C interrupt status register (ICSTR) is used to determine which interrupt has occurred and to read status information.

The I2C interrupt status register (ICSTR) is shown in Figure 15 and described in Table 7.

Figure 15. I2C Interrupt Status Register (ICSTR)

31 |

|

|

|

|

|

|

|

| 16 |

|

|

|

| Reserved |

|

|

| ||

|

|

|

|

|

|

|

| ||

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | ||

|

|

|

|

|

|

|

|

|

|

Reserved |

| SDIR | NACKSNT | BB |

| RSFULL | XSMT | AAS | AD0 |

|

| ||||||||

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | ||

|

|

|

|

|

|

|

|

| |

Reserved | SCD | ICXRDY |

| ICRRDY | ARDY | NACK | AL | ||

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

LEGEND: R/W = Read/Write; R = Read only; W1C = Write 1 to clear (writing 0 has no effect);

Table 7. I2C Interrupt Status Register (ICSTR) Field Descriptions

Bit | Field |

| Value | Description |

|

|

|

|

|

|

|

Reserved |

| 0 | These reserved bit locations are always read as zeros. A value written to this field has no effect. |

| |

|

|

|

|

|

|

14 | SDIR |

|

| Slave direction bit. In |

|

|

|

| 0 | I2C is acting as a |

|

|

|

|

| following events: |

|

|

|

|

| • A STOP or a START condition. |

|

|

|

|

| • SDIR is manually cleared. To clear this bit, write a 1 to it. |

|

|

|

| 1 | I2C is acting as a |

|

|

|

|

|

| |

13 | NACKSNT |

|

| ||

|

|

|

| in which NACKSNT is affected is when the NACK mode is used (see the description for NACKMOD in |

|

|

|

|

| Section 3.9). |

|

|

|

| 0 | NACK is not sent. NACKSNT is cleared by one of the following events: |

|

|

|

|

| • It is manually cleared. To clear this bit, write a 1 to it. |

|

|

|

|

| • The I2C is reset (either when 0 is written to the IRS bit of ICMDR or when the processor is reset). |

|

|

|

| 1 | NACK is sent. A |

|

|

|

|

|

|

|

12 | BB |

|

| Bus busy bit. BB bit indicates whether the |

|

|

|

|

| master mode, BB is controlled by the software. |

|

|

|

| 0 | Bus is free. BB is cleared by one of the following events: |

|

|

|

|

| • The I2C receives or transmits a STOP bit (bus free). |

|

|

|

|

| • BB is manually cleared. To clear this bit, write a 1 to it. |

|

|

|

|

| • The I2C is reset (either when 0 is written to the IRS bit of ICMDR or when the processor is reset). |

|

|

|

| 1 | Bus is busy. When the STT bit in ICMDR is set to 1, a restart condition is generated. BB is set by one of | |

|

|

|

| the following events: |

|

|

|

|

| • The I2C has received or transmitted a START bit on the bus. |

|

|

|

|

| • SCL is in a low state and the IRS bit in ICMDR is 0. |

|

|

|

|

|

|

|

11 | RSFULL |

|

| Receive shift register full bit. RSFULL indicates an overrun condition during reception. Overrun occurs |

|

|

|

|

| when the receive shift register (ICRSR) is full with new data but the previous data has not been read |

|

|

|

|

| from the data receive register (ICDRR). The new data will not be copied to ICDRR until the previous |

|

|

|

|

| data is read. As new bits arrive from the SDA pin, they overwrite the bits in ICRSR. |

|

|

|

| 0 | No overrun is detected. RSFULL is cleared by one of the following events: |

|

|

|

|

| • ICDRR is read. |

|

|

|

|

| • The I2C is reset (either when 0 is written to the IRS bit of ICMDR or when the processor is reset). |

|

|

|

| 1 | Overrun is detected. |

|

|

|

|

|

|

|

|

|

|

|

|

|

SPRUEN0D |

| 25 | |||

Submit Documentation Feedback |

|

| |||

© 2011, Texas Instruments Incorporated