Registers | www.ti.com |

3.12 I2C Prescaler Register (ICPSC)

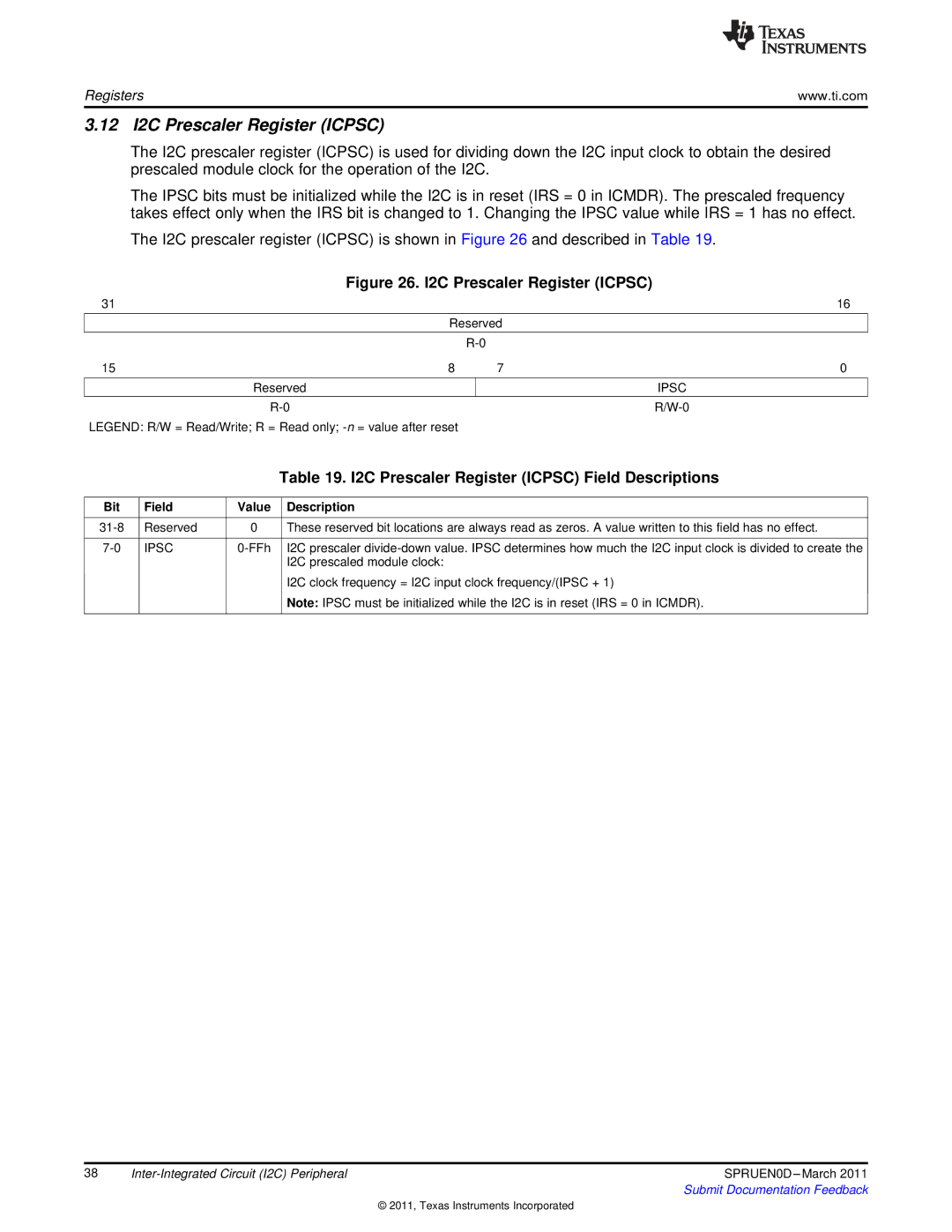

The I2C prescaler register (ICPSC) is used for dividing down the I2C input clock to obtain the desired prescaled module clock for the operation of the I2C.

The IPSC bits must be initialized while the I2C is in reset (IRS = 0 in ICMDR). The prescaled frequency takes effect only when the IRS bit is changed to 1. Changing the IPSC value while IRS = 1 has no effect.

The I2C prescaler register (ICPSC) is shown in Figure 26 and described in Table 19.

Figure 26. I2C Prescaler Register (ICPSC)

31 |

|

|

| 16 |

| Reserved |

| ||

|

|

|

| |

|

|

| ||

15 | 8 | 7 | 0 | |

|

|

|

|

|

| Reserved |

|

| IPSC |

|

|

|

|

|

|

|

| ||

LEGEND: R/W = Read/Write; R = Read only;

|

|

| Table 19. I2C Prescaler Register (ICPSC) Field Descriptions | |

|

|

|

|

|

Bit | Field | Value |

| Description |

|

|

|

|

|

Reserved | 0 |

| These reserved bit locations are always read as zeros. A value written to this field has no effect. | |

|

|

|

|

|

IPSC |

| I2C prescaler | ||

|

|

|

| I2C prescaled module clock: |

|

|

|

| I2C clock frequency = I2C input clock frequency/(IPSC + 1) |

|

|

|

| Note: IPSC must be initialized while the I2C is in reset (IRS = 0 in ICMDR). |

|

|

|

|

|

38 | SPRUEN0D | |

|

| Submit Documentation Feedback |

© 2011, Texas Instruments Incorporated