www.ti.com | Peripheral Architecture |

2.6Serial Data Formats

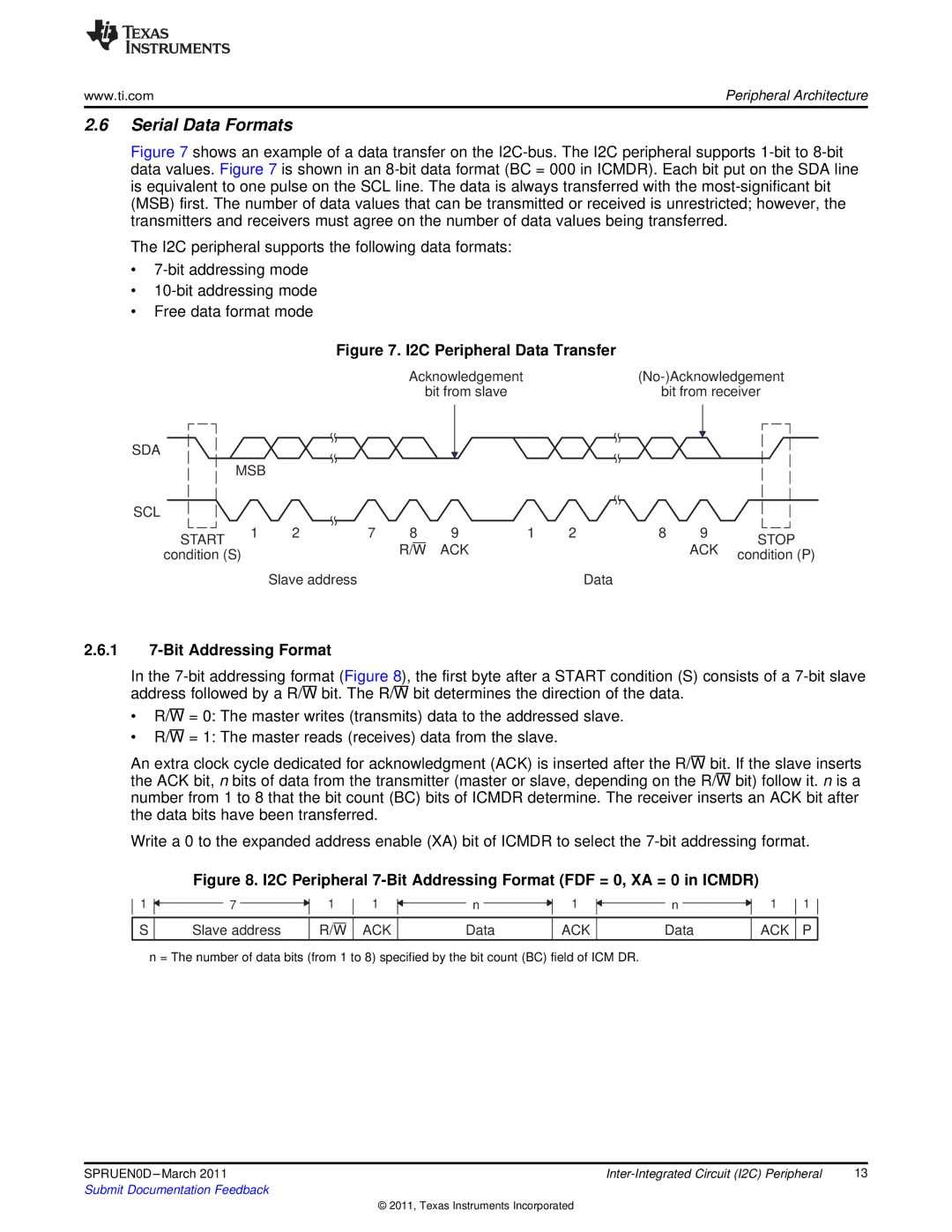

Figure 7 shows an example of a data transfer on the I2C-bus. The I2C peripheral supports 1-bit to 8-bit data values. Figure 7 is shown in an 8-bit data format (BC = 000 in ICMDR). Each bit put on the SDA line is equivalent to one pulse on the SCL line. The data is always transferred with the most-significant bit (MSB) first. The number of data values that can be transmitted or received is unrestricted; however, the transmitters and receivers must agree on the number of data values being transferred.

The I2C peripheral supports the following data formats:

•7-bit addressing mode

•

•Free data format mode

Figure 7. I2C Peripheral Data Transfer

|

|

|

| Acknowledgement |

|

| ||||

|

|

|

| bit from slave |

|

| bit from receiver | |||

SDA |

|

|

|

|

|

|

|

|

|

|

| MSB |

|

|

|

|

|

|

|

|

|

SCL |

|

|

|

|

|

|

|

|

|

|

START | 1 | 2 | 7 | 8 | 9 | 1 | 2 | 8 | 9 | STOP |

|

|

| R/W | ACK |

|

|

| ACK | ||

condition (S) |

|

|

|

|

| condition (P) | ||||

|

|

|

|

|

|

|

| |||

|

| Slave address |

|

|

|

|

| Data |

|

|

2.6.17-Bit Addressing Format

In the

•R/W = 0: The master writes (transmits) data to the addressed slave.

•R/W = 1: The master reads (receives) data from the slave.

An extra clock cycle dedicated for acknowledgment (ACK) is inserted after the R/W bit. If the slave inserts the ACK bit, n bits of data from the transmitter (master or slave, depending on the R/W bit) follow it. n is a number from 1 to 8 that the bit count (BC) bits of ICMDR determine. The receiver inserts an ACK bit after the data bits have been transferred.

Write a 0 to the expanded address enable (XA) bit of ICMDR to select the

Figure 8. I2C Peripheral 7-Bit Addressing Format (FDF = 0, XA = 0 in ICMDR)

1

7

1

1

n

1

n

1

1

S

Slave address

R/W ACK

Data

ACK

Data

ACK P

n = The number of data bits (from 1 to 8) specified by the bit count (BC) field of ICM DR.

SPRUEN0D | 13 | |

Submit Documentation Feedback |

|

|

© 2011, Texas Instruments Incorporated