Peripheral Architecture | www.ti.com |

2.9NACK Bit Generation

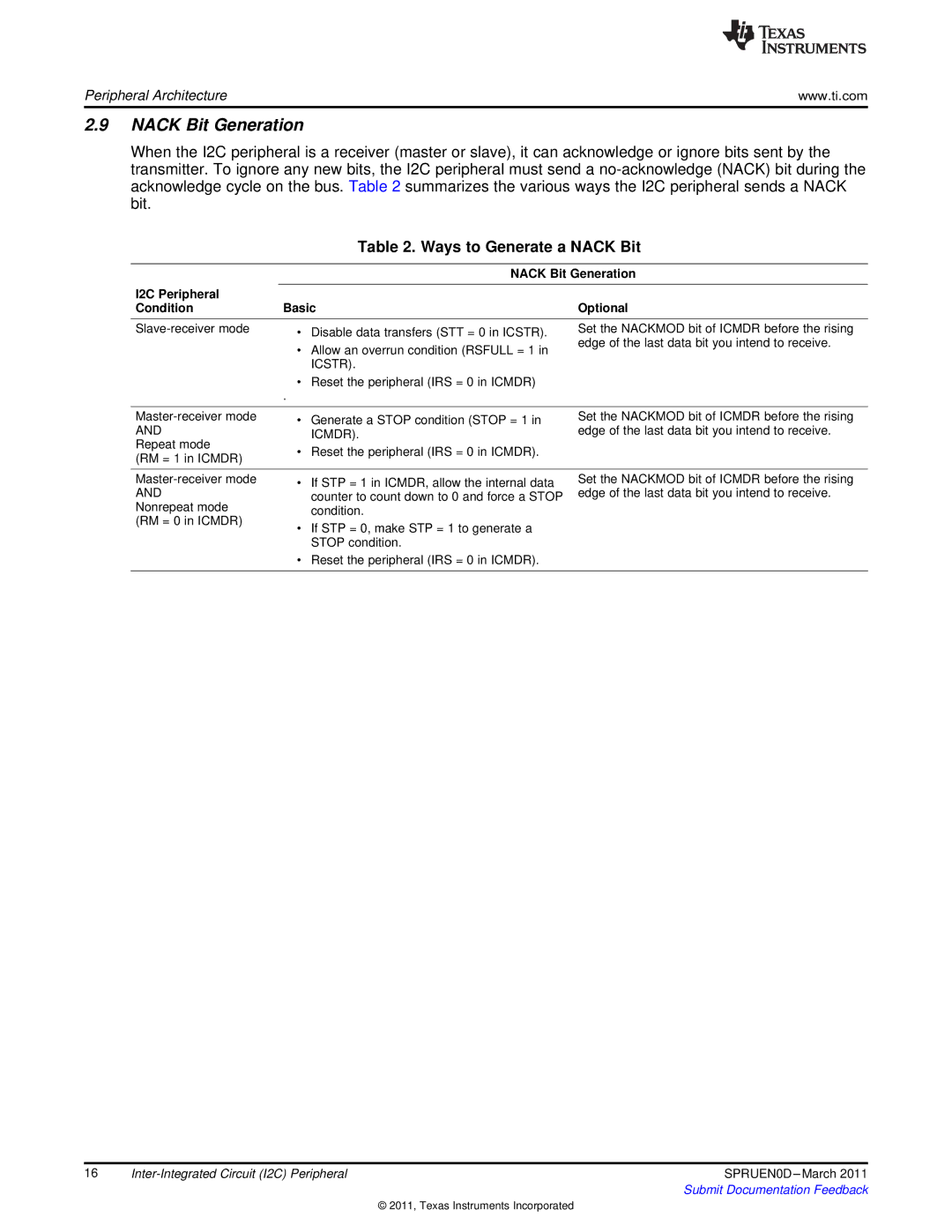

When the I2C peripheral is a receiver (master or slave), it can acknowledge or ignore bits sent by the transmitter. To ignore any new bits, the I2C peripheral must send a

| Table 2. Ways to Generate a NACK Bit | ||

|

| ||

| NACK Bit Generation | ||

I2C Peripheral |

|

| |

|

| ||

Condition | Basic | Optional | |

|

|

| |

• Disable data transfers (STT = 0 in ICSTR). | Set the NACKMOD bit of ICMDR before the rising | ||

| edge of the last data bit you intend to receive. | ||

| • Allow an overrun condition (RSFULL = 1 in | ||

|

| ||

| ICSTR). |

| |

| • Reset the peripheral (IRS = 0 in ICMDR) |

| |

| . |

| |

|

|

| |

• Generate a STOP condition (STOP = 1 in | Set the NACKMOD bit of ICMDR before the rising | ||

AND | edge of the last data bit you intend to receive. | ||

ICMDR). | |||

Repeat mode |

| ||

• Reset the peripheral (IRS = 0 in ICMDR). |

| ||

(RM = 1 in ICMDR) |

| ||

|

| ||

|

|

| |

• If STP = 1 in ICMDR, allow the internal data | Set the NACKMOD bit of ICMDR before the rising | ||

AND | edge of the last data bit you intend to receive. | ||

counter to count down to 0 and force a STOP | |||

|

| ||

Nonrepeat mode | condition. | |

(RM = 0 in ICMDR) | ||

• If STP = 0, make STP = 1 to generate a | ||

| ||

| STOP condition. | |

| • Reset the peripheral (IRS = 0 in ICMDR). | |

|

|

16 | SPRUEN0D | |

|

| Submit Documentation Feedback |

© 2011, Texas Instruments Incorporated