www.ti.com

Peripheral Architecture

2.9Refresh Scheduling

The DDR2 memory controller issues autorefresh (REFR) commands to DDR2 SDRAM devices at a rate defined in the refresh rate (RR) bit field in the SDRAM refresh control register (SDRCR). A refresh interval counter is loaded with the value of the RR bit field and decrements by 1 each cycle until it reaches zero. Once the interval counter reaches zero, it reloads with the value of the RR bit. Each time the interval counter expires, a refresh backlog counter increments by 1. Conversely, each time the DDR2 memory controller performs a REFR command, the backlog counter decrements by 1. This means the refresh backlog counter records the number of REFR commands the DDR2 memory controller currently has outstanding.

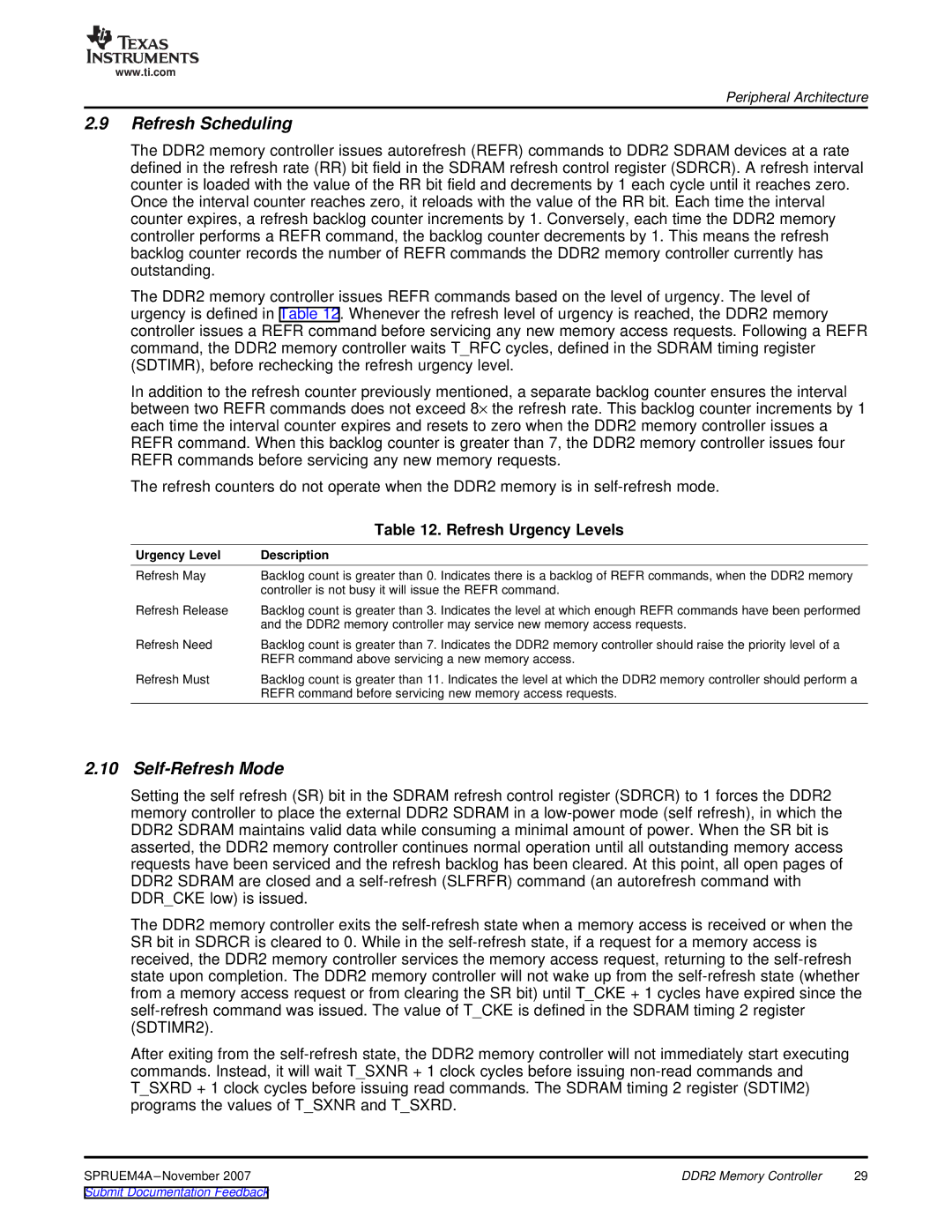

The DDR2 memory controller issues REFR commands based on the level of urgency. The level of urgency is defined in Table 12. Whenever the refresh level of urgency is reached, the DDR2 memory controller issues a REFR command before servicing any new memory access requests. Following a REFR command, the DDR2 memory controller waits T_RFC cycles, defined in the SDRAM timing register (SDTIMR), before rechecking the refresh urgency level.

In addition to the refresh counter previously mentioned, a separate backlog counter ensures the interval between two REFR commands does not exceed 8× the refresh rate. This backlog counter increments by 1 each time the interval counter expires and resets to zero when the DDR2 memory controller issues a REFR command. When this backlog counter is greater than 7, the DDR2 memory controller issues four REFR commands before servicing any new memory requests.

The refresh counters do not operate when the DDR2 memory is in

| Table 12. Refresh Urgency Levels |

Urgency Level | Description |

Refresh May | Backlog count is greater than 0. Indicates there is a backlog of REFR commands, when the DDR2 memory |

| controller is not busy it will issue the REFR command. |

Refresh Release | Backlog count is greater than 3. Indicates the level at which enough REFR commands have been performed |

| and the DDR2 memory controller may service new memory access requests. |

Refresh Need | Backlog count is greater than 7. Indicates the DDR2 memory controller should raise the priority level of a |

| REFR command above servicing a new memory access. |

Refresh Must | Backlog count is greater than 11. Indicates the level at which the DDR2 memory controller should perform a |

| REFR command before servicing new memory access requests. |

2.10 Self-Refresh Mode

Setting the self refresh (SR) bit in the SDRAM refresh control register (SDRCR) to 1 forces the DDR2 memory controller to place the external DDR2 SDRAM in a

The DDR2 memory controller exits the

After exiting from the

DDR2 Memory Controller | 29 |