www.ti.com

DDR2 Memory Controller Registers

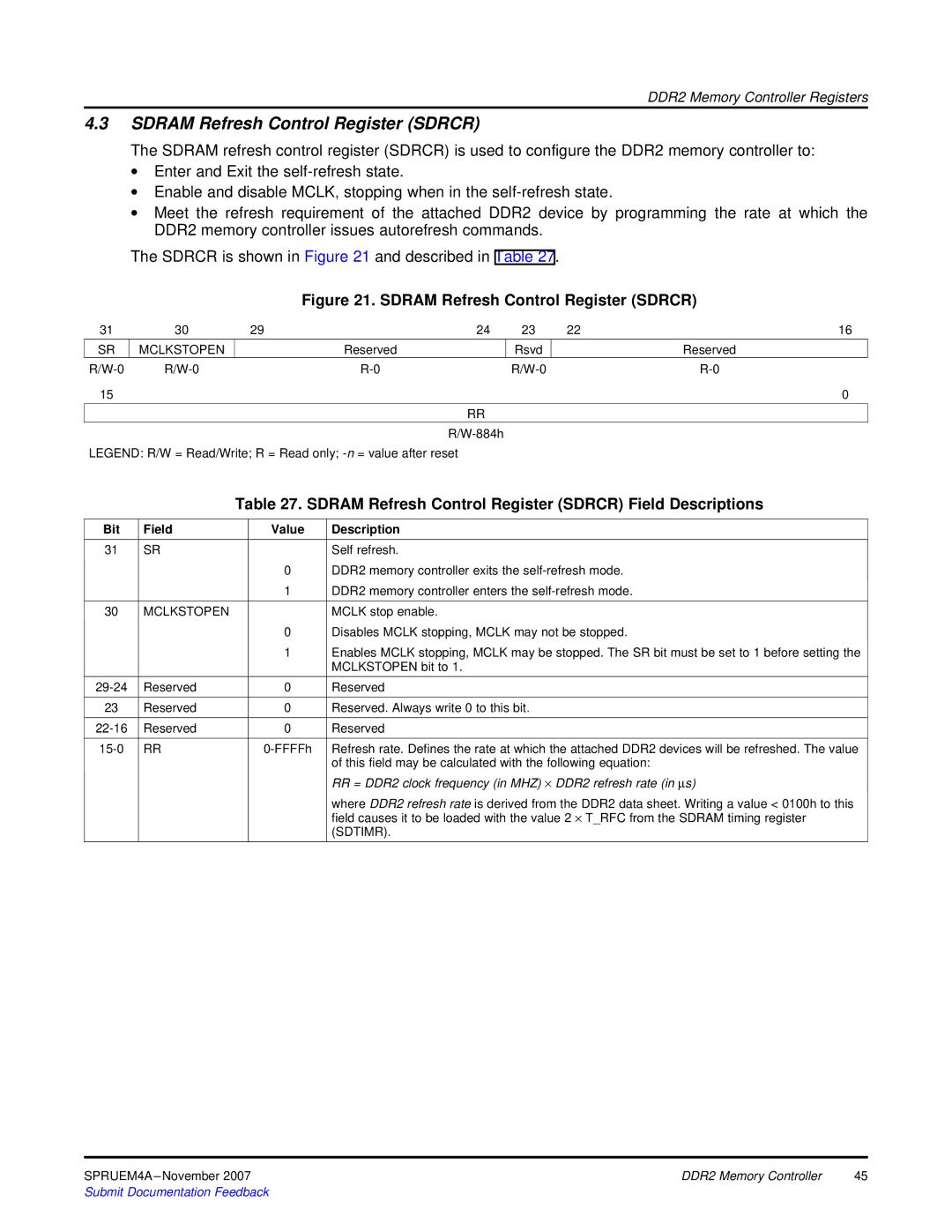

4.3SDRAM Refresh Control Register (SDRCR)

The SDRAM refresh control register (SDRCR) is used to configure the DDR2 memory controller to:

∙Enter and Exit the

∙Enable and disable MCLK, stopping when in the

∙Meet the refresh requirement of the attached DDR2 device by programming the rate at which the DDR2 memory controller issues autorefresh commands.

The SDRCR is shown in Figure 21 and described in Table 27.

Figure 21. SDRAM Refresh Control Register (SDRCR)

31 | 30 | 29 | 24 | 23 | 22 | 16 |

SR | MCLKSTOPEN |

| Reserved | Rsvd |

| Reserved |

|

| |||||

15 |

|

|

|

|

| 0 |

|

|

| RR |

|

|

|

|

|

|

|

|

| |

LEGEND: R/W = Read/Write; R = Read only; |

|

|

| |||

Table 27. SDRAM Refresh Control Register (SDRCR) Field Descriptions

Bit | Field | Value | Description |

31 | SR |

| Self refresh. |

|

| 0 | DDR2 memory controller exits the |

|

| 1 | DDR2 memory controller enters the |

30 | MCLKSTOPEN |

| MCLK stop enable. |

|

| 0 | Disables MCLK stopping, MCLK may not be stopped. |

|

| 1 | Enables MCLK stopping, MCLK may be stopped. The SR bit must be set to 1 before setting the |

|

|

| MCLKSTOPEN bit to 1. |

Reserved | 0 | Reserved | |

23 | Reserved | 0 | Reserved. Always write 0 to this bit. |

Reserved | 0 | Reserved | |

RR |

| Refresh rate. Defines the rate at which the attached DDR2 devices will be refreshed. The value |

of this field may be calculated with the following equation:

RR = DDR2 clock frequency (in MHZ) × DDR2 refresh rate (in μs)

RR = DDR2 clock frequency (in MHZ) × DDR2 refresh rate (in μs)

where DDR2 refresh rate is derived from the DDR2 data sheet. Writing a value < 0100h to this field causes it to be loaded with the value 2 × T_RFC from the SDRAM timing register (SDTIMR).

DDR2 Memory Controller | 45 | |

Submit Documentation Feedback |

|

|